瑞萨电子精简数据中心的存储器组件数量

来源:华强电子网 作者: 时间:2016-07-11 09:01

全球领先的半导体解决方案供应商瑞萨电子株式会社(TSE:6723)今日宣布推出一种面向100Gb通信设备,如路由器、交换机和服务器的数据包标题搜索参考设计。

该瑞萨电子参考设计由LLDRAM-III (RMHE41A364AGBG)高功效、低延时存储器(LLDRAM)、专有精确匹配搜索IP和FPGA(注1)设备上的LLDRAM-III控制器IP,以及开发支持工具组成。它使用的存储设备数量仅为采用标准DRAM存储器的配置中所需设备的1/15,却能实现100Gb流量的数据包标题搜索功能,并将存储器功耗降低60%。

随着物联网(IoT)时代的到来和连接设备所接收和发送数据量的快速增加,提高网络速度已成为当务之急。尤其是有更多的数据中心将其流量速度从40Gb切换至100Gb,以支持不断增加的数据量和搜索条目数量。但是,提高网络设备的速度通常会导致功耗增加,产生设备包温度和电力成本等问题。此外,SDN和NFV的广泛应用要求频繁通过软件修改网络配置,而且需要使用支持灵活重新配置的网络设备。在这一背景下,瑞萨电子开发了高功效、可处理高速流量的数据包标题搜索参考设计。它采用了FPGA技术,可进行灵活的网络配置,并拥有可存储一百万或更多搜索条目的LLDRAM-III存储器。

数据包标题搜索参考设计的主要特点:

(1) 仅消耗2瓦,相当于40Gb流量的功耗,即可以100Gb流量进行一百万次或更多(注2)的数据包标题搜索输入

LLDRAM-III是瑞萨电子推出的一种高功效、低延时存储器,支持每秒400兆次存取(读取或写入操作),传输57.6 Gb数据所需的功率仅为2瓦或更低。将该存储器与瑞萨电子新开发的搜索算法相结合,使用单个LLDRAM-III设备每秒可以处理1.5亿次数据包标题搜索,达到100Gb以太网的要求。而使用传统搜索算法(注3)和标准DRAM的配置进行同样的处理,则需要大约15个存储设备,功耗大约为5瓦(注4)。该新型参考设计将存储设备数量减少为单个LLDRAM-III存储器,并将存储器功耗降低60%。这样能够将存储器安装面积和存储器与FPGA之间的信号线数量均减少90%,因此可以使用一个少管脚的FPGA配置系统并有助于降低整体成本。

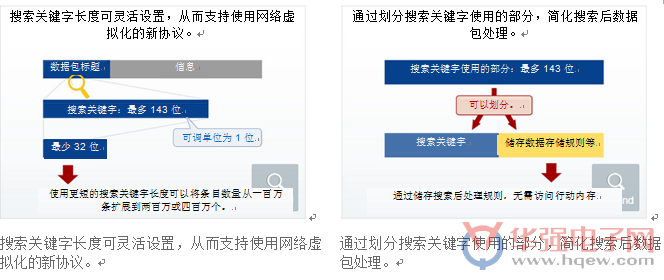

(2) 灵活的搜索关键字长度功能,无需改动搜索IP设计即可适应新通信协议

精确匹配的搜索IP可灵活改变搜索关键字长度,以1位为单位,最多可达143位(注5)。在不修改搜索IP设计的情况下,不仅能适应常规的MAC地址搜索,还能适应通过网络虚拟技术进步实现的新通信协议。此外,可通过指定更短的最大搜索关键字(注6)长度,将搜索条目的数量扩展到二百万个甚至四百万个。在使用143位的最大搜索关键字长度时,还可通过划分搜索结果所附加的搜索关键字区域和数据包处理规则区域,支持同时输出搜索结果和数据包处理规则。

(3) 完全集成的参考设备工具包可将网络设备设计所需的开发时间缩短大约六个月

开发支持工具包括1) 一个参考板,在FPGA和LLDRAM-III之间具有成熟的互操作性,从而节省设计和验证所需的时间,2) 包括搜索IP的设计样本,3) 完整的验证环境,4) 完整的评估环境。借助这些工具,用户可以同步启动FPGA子系统设计和网络设备设计,从而将开发周期时间大幅缩短约六个月(根据瑞萨电子的计算结果)。

本文为华强电子网原创,版权所有,转载需注明出处

关注电子行业精彩资讯,关注华强资讯官方微信,精华内容抢鲜读,还有机会获赠全年杂志

关注方法:添加好友→搜索“华强微电子”→关注

或微信“扫一扫”二维码

下一篇:矽睿科技为国产手机提供更精确导航

- •突涨25%!FPGA交期“见顶”,汽车、数据中心、工业需求高涨2022-11-24

- •传英特尔调涨部分FPGA价格最高20%2022-07-22

- •BittWare宣布合作伙伴计划,为基于FPGA的解决方案降低创新风险缩短上市时间2022-04-21

- •FPGA“上位”之后:一场国产替代与人才的“世纪纠结”?2021-11-29

- •成就中国FPGA第一股 安路成功登陆科创板2021-11-12

- •华大半导体入股 成都一FPGA公司拟谋求上市!曾经历三轮融资2021-10-18

- •FPGA如何称霸工业和汽车视觉市场?2021-07-07

- •京微齐力:FPGA实现国产自主可控,稳固消费市场冲击高端2021-05-14

- •Achronix宣布其业界性能最高的Speedster7t FPGA器件现已开始供货2021-04-29

- •首次支持RISC-V!莱迪思新方案如何降低FPGA视觉与安全应用开发难度?2021-03-29