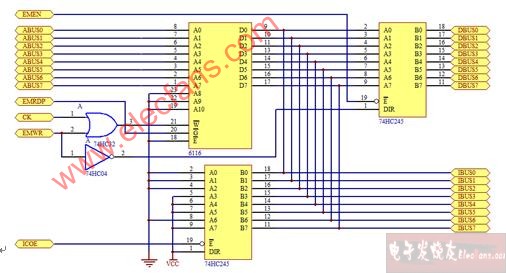

存储器EM原理图

来源:电子发烧友 作者:华强电子网 时间:2019-01-23 11:09

存储器EM原理图

存储器EM的地址可以选择由PC或MAR提供。当读取EM中的指令时,其地址由PC提供;当读取EM中的操作数时,其地址由MAR提供。

5、实验内容与步骤

(1)、按照表2-12连线。

表 2-12 存储器EM实验连线表

连接 信号孔 接入孔 作用 有效电平

1 J2座 J3座 将K23-K16接入DBUS[7:0]

2 IREN K6 IR, uPC写允许 低电平有效

3 PCOE K5 PC输出地址 低电平有效

4 MAROE K4 MAR输出地址 低电平有效

5 MAREN K3 MAR写允许 低电平有效

6 EMEN K2 存储器与数据总线相连 低电平有效

7 EMRD K1 存储器读允许 低电平有效

8 EMWR K0 存储器写允许 低电平有效

9 PCCK CLOCK PC工作脉冲 上升沿打入

10 MARCK CLOCK MAR工作脉冲 上升沿打入

11 EMCK CLOCK 写脉冲 上升沿打入

12 IRCK CLOCK IR, uPC工作脉冲 上升沿打入

上一篇:微程序存储器uM的原理图

下一篇:uPC(八位带预置计数器)原理图

- •下行周期下实现逆势增长!这家存储器新锐企业是如何做到的?2023-03-31

- •新思科技推出最新解决方案,加速存储器、AI、汽车和5G应用高收敛IC设计2021-05-10

- •芯片供应紧张将持续数年 存储器价格上涨趋势不改2021-01-29

- •应用材料公司推出用于先进存储器和逻辑芯片的新型刻蚀系统Sym32020-08-10

- •高速数据与高带宽存储器支持带来卓越高速计算体验2020-07-02

- •集邦咨询:中国存储器厂均正常运作 武汉疫情未造成供给问题2020-02-04

- •全球唯一“存储器藏逻辑”力晶推革命性架构AIM2019-12-05

- •Microchip全新EERAM存储器解决方案,可降低存储器成本并在断电时 提供数据保护2019-12-04

- •贵州增添“芯”实力,打造非易失存储器AI芯片等项目2019-11-01

- •存储器市况好转,力成首见“第4季仍在扩产”2019-10-23