用ClearNAND闪存改善系统设计

来源:华强LED网 作者:—— 时间:2011-02-16 16:07

自问世以来,NAND闪存对ECC(纠错码)纠错能力的要求越来越高。虽然这不是一个新问题,但是支持最新的多层单元(MLC)架构和每单元存储三位数据(three-bit-per-cell)技术所需的ECC纠错能力让系统人员越来越难以应付。

过去,ECC一直被用于提高NAND闪存子系统的整体数据可靠性。但是,随着NAND单元不断缩小,每个浮栅内贮存的电子数量越来越少。因此,为弥补更小的存储单元所产生的更高的位误码率,我们必须大幅提高ECC纠错能力,以维持所需的系统可靠性。

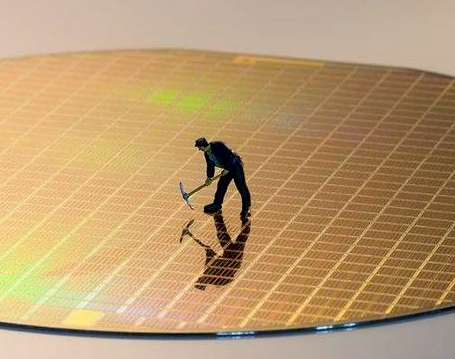

随着系统对ECC纠错要求不断提高,实现ECC逻辑所需的逻辑门数量也在增加,同时系统复杂性也随之提高。例如,24位ECC需要大约200,000个逻辑门,而40位ECC则需要大约300,000个逻辑门。据估计,将来先进的ECC算法可能需要近100万个逻辑门(如图1所示)。

很多高性能闪存系统必须使用多通道NAND闪存才能实现理想的性能。在这些系统中,每个通道都有其自己的ECC逻辑。例如,一个10通道固态硬盘(SSD)需要实现10通道的ECC逻辑。假如10路通道中的每一路通道都需要60位ECC,那么仅ECC逻辑就需要300万个逻辑门。

NAND闪存接口选择

1.传统NAND接口

传统的NAND闪存接口是一种异步通信接口,虽然近几年这种接口的速度已提高到50MHz,但是其它特性并没有太大的变化。

几年前,美光(Micron)与其它几家富有远见的公司共同成立了一家NAND闪存组织,旨在简化业界存在的大量时序和指令标准。开放式NAND闪存接口(ONFI)联盟发布了其第一版ONFI 1.0规范,与最初的规范相比,这个接口规范的最大特点是主处理器能够通过电子方式识别所连接的闪存类型,以及其它重要的技术参数,如时序模式、页面大小、块大小、ECC要求等。该特性被所有的ONFI标准继承下来,并且一直是所有ONFI标准的重要内容。

同步NAND接口的开发是ONFI联盟取得的另一个重要成就,这一接口规范又称为ONFI 2。目前,ONFI 2.2规范通过一个DDR源同步接口支持高达每秒20000万次传输(200MT/s)。通电后该接口可用于异步通信模式。但是,对于更高的性能而言,当从异步模式转换到同步通信模式时,主处理器会提前询问闪存设备是否支持更高速的同步通信接口。

- •艾笛森力推全方位LED照明整合服务方案2012-12-13

- •BCD推出最高功率因子LED驱动解决方案2012-09-14

- •DAS为LED工业开发创新型废气解决方案2012-09-14

- •BCD Semi推出高功率因子LED驱动电源解决方案2012-09-13

- •红外LED在安防监控摄像机中运用的误区2012-08-27

- •估算LED寿命 LM-80与TM-21谁更准确2012-08-15

- •浅谈LED显示屏之LED驱动电源隔离之间的差异2012-08-13

- •飞兆半导体解决方案加速LED照明节能进程2012-08-13

- •欧司朗:高显指高光效混色LED方案2012-08-10

- •LED芯片及封装专利布局和卡位2012-08-09