ARM的“大-小核”架构日子要到头了吗?

来源:华强电子网 作者:—— 时间:2013-04-02 10:16

在早期的数字电子技术时代,能够实现的卓越架构以及这种架构所带来的优势可以应用于几乎所有可预见的多代制造工艺节点。但现在芯片制造的复杂性和变化是如此之大,以致于一些优秀的想法和技术如果不经过彻底的改造就很难维持下去。

“大-小(Big-little)核”这种架构出自处理器授权商ARM有限公司(英国剑桥),是指成对使用针对性能优化过的处理器内核和针对低功耗待机优化过的处理器内核。它能帮助应用软件在两个内核之间切换,从而在设备大部分时间处于待机模式的典型使用情况下实现总体能耗节省。为了实现这一策略,ARM准备了两种处理器内核,即Cortex-A15和Cortex-A7,而且这种架构已经开始在商用产品中成功实现。如瑞萨移动公司(RenesasMobile)的MP6530。

但是,大-小核架构能持续吗?如果不能,必须要进行怎样的彻底改造呢?

首先,我们必须承认大-小核架构本身是对动态电压与频率调节(DVFS)的彻底改造或补充。

动态电压与频率调节技术指的是,您可以在需要低性能时调低给定内核的电压与时钟频率,以节省动态功耗,然后在需要达到必要的高应用性能等级时调高电压与时钟频率。因此应用程序通常在Cortex-A7上启动,然后通过DVFS“装置”逐渐提升性能,直到达到最高电压和最大时钟频率。接着跳接到Cortex-A15上以较低电压和较低功耗继续运行,然后再次通过DVFS装置提升性能直到最大。当应用负载消失时,反向执行这一过程,直到设备再次回到空闲状态,在“小”内核上以最低DVFS点运行。

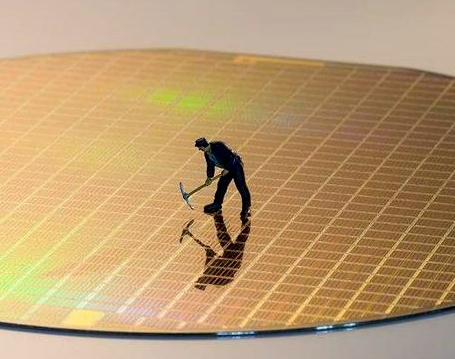

然而,随着我们遵循摩尔定律实现了更小的尺寸,同时也减少了电压范围,因而减少了DVFS的可扩展性。因此ARM的聪明想法是利用额外的硅片面积补偿DVFS的这些缺陷。

但如果我们继续遵循摩尔定律实现20nmBulkCMOS和16/14nmFinFET工艺时,电压的可扩展性可能还会进一步减小,从而减小在大-小核架构中使用DVFS的范围。此时我们该怎么办呢?

更多内核,还是更多DVFS,或者两者兼顾?

面对上述问题,两个内核的大-小核架构可能就行不通了,ARM需要找出一种粒度更加精细的方法来。使用针对不同的节能与性能等级优化的一整套ISA兼容内核也许是个不错的主意。它会演变成“最大-大-小-微型”策略吗?

但硅片占用面积会怎样?如果让经过优化的ISA兼容内核全部等待在功耗-性能曲线中的某个特定点运行,这种复杂的层次结构是否太过于昂贵呢?

也许是,也许不是。我们应该还记得,大-小核架构在一定程度上也是对ARM“暗硅”说法的一种回应。暗硅指的是基于功耗和散热的原因,高级处理器无法忍受所有硅片在同一时刻同时工作,否则芯片会烧毁。因此一种主张是仍然使用针对不同负载和使用情况优化的IC不同部分。反对的意见认为,与其设计一个暗硅占主要部分的复杂IC,还不如设计一个更加简单、制造成本也更低的芯片。

一种替代方案是找到一种能够支持更宽范围DVFS的制造工艺。

事实上,这种工艺已经存在,比如意法半导体公司(ST)的28nm全耗尽型绝缘硅(FDSOI)制造工艺。这种工艺可以将工作电压降低至大约0.6V,而相比之下BulkCMOS工艺的最小极限值一般在0.9V左右。使用FDSOI的后向偏置技术可以提供更宽动态范围的性能,因此应该能够很好地适应大-小核架构。

事实上,意法-爱立信(ST-Ericsson)已经使用28nmFDSOI向市场推出了一款“四核”的处理器?L8580ModAp,这款处理器基于两个物理Cortex-A9内核。意法-爱立信公司的想法是,Cortex-A9可以在低电压下工作,因此可以像“小”内核一样节省动态功耗,或者像“大”内核那样通过提高时钟频率来推高性能。这是一种虚拟的大-小核架构。

我不太喜欢用虚拟内核的数量来衡量一颗芯片,而这似乎成了当今的一种趋势,原因当然是这个数字可以是任意的。我更愿意在三维物理空间中计算内核的数量。

虽然如此,时间分片、扩展的DFVS和多个物理内核的更智能的组合可能将成为大-小核架构在我们已有的多维扩展空间中向前发展的一种方式。

下一篇:毫米波元件的最新技术进展

- •重磅!美断供中国芯片架构或被打脸!2023-10-09

- •年出货量超100亿颗!该架构的芯片在下游终端进展迅猛2023-05-05

- •最新趋势!Arm架构芯片将抢占大部分云服务器和PC市场2022-11-22

- •国内芯片厂商翻身机会!RISC-V与arm决战在全球半导体变局中2022-07-14

- •全志科技基于RISC- V架构内核开发的D1芯片已经实现量产2021-12-27

- •龙芯自主指令集架构,“国产之光”还是“PPT式胜利”?2021-04-23

- •官宣!百度汽车吉利架构,领涨四方谁能笑到最后?2021-01-11

- •瑞萨电子开发其首款RISC-V架构ASSP产品2020-10-12

- •取代Intel!苹果Mac设备全线迁移ARM可行性有多大?2020-03-28

- •x86+ARM混合架构?Xbox Series X将首发迄今最复杂SoC2020-03-16