5nm不是梦!IMEC与Cadence完成首款5纳米测试芯片的成功流片

来源:我爱研发网 作者:------ 时间:2015-10-15 11:28

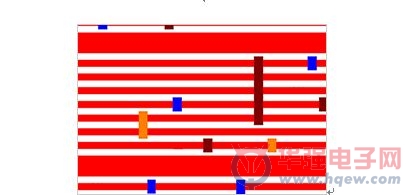

2015年10月14日——比利时微电子研究中心imec与全球电子设计创新领先企业Cadence设计系统公司今天共同宣布,使用极紫外光(EUV)及193浸式(193i)光刻技术,两家公司携手完成对5纳米测试芯片的第一次成功流片。为生产该测试芯片,imec与Cadence对设计规则、单元库及布局布线进行了全面优化,并使用Cadence? Innovus? 设计实现系统达成对功耗、性能和面积(PPA)的最优化方案。利用处理器设计、EUV光刻及用于193i光刻的自对准四重图案成型技术(Self- Aligned Quadruple Patterning, SAQP),imec和Cadence成功完成一组流片的设计和测试。流片加工过程中,金属间距由公称32nm减至24nm,将间距排列推向新的极致。

设计实现系统是下一代物理设计实现解决方案,系统芯片(SoC)开发人员可以在保证最佳功耗、性能和面积(PPA)的前提下缩短上市时间。得益于大规模并行架构带来的突破性优化技术,Innovus设计实现系统可以在功耗、性能和面积(PPA)指标上提升10% 到20%,并实现最高达10倍的全流程提速和容量增益。

“开发5nm及以下高阶几何排列的过程中,与Cadence的合作发挥了关键作用。”imec制程技术资深副总裁An Steegen表示:“我们共同开发了核心技术,使该测试芯片使用高阶技术节点成功流片成为现实。Cadence的下一代平台使用便捷,为工程团队高效完成高级节点工艺规则的设计奠定了基础。”

“鉴于双方合作所取得的里程碑式胜利,Cadence与imec将继续致力于推动将金属间距排列技术应用在越来越小的节点上”。Cadence数字与 Signoff事业部资深副总裁Anirudh Devgan博士表示:“imec技术及Cadence的Innovus设计实现系统开创出我们独有的设计流程,为新一代创新型移动与计算机高级节点设计的开发奠定了坚实基础。”

参与Qualcomm调研活动100%中大奖哦!小伙伴们快点行动吧!

关注方法:添加好友→搜索“华强微电子”→关注

或微信“扫一扫”二维码

- •重磅!中国或禁止政府采购这类芯片和品牌2024-03-25

- •2024年全球芯片终端客户订单情况及趋势预判2024-03-22

- •最新PMIC芯片市场竞争格局、供应商及发展趋势2024-03-19

- •出货量翻50多倍!这类芯片涨价20%!村田/ST/微芯/华邦电等最新现货行情 | 周行情137期2024-03-18

- •对标ST!这家国产厂商的该类芯片加速上车2024-03-15

- •马来西亚芯片的崛起2024-03-14

- •这些芯片,将大幅涨价2024-03-11

- •CITE2024开展倒计时 等你来看大模型、芯片、机器人、智能驾驶……2024-03-04

- •裁员潮!这些品类芯片售罄!ST/微芯/华邦等最新现货行情 | 周行情135期2024-03-04

- •装载或超百万辆!这类芯片正在汽车领域加速渗透2024-02-23