支持硬核浮点DSP的FPGA或可取代高性能计算GPGPU

来源:华强电子网 作者:------ 时间:2014-07-02 14:46

近来,Altera公司推出业界首款浮点FPGA,它集成了硬核IEEE 754兼容浮点运算功能,提高了DSP性能、设计人员的效能和逻辑效率。据悉,硬核浮点DSP模块集成在Altera 20nm Arria 10 FPGA和SoC中,以及14nm Stratix 10 FPGA和SoC中。该新功能支持设计人员以相同的定点性能和效率在浮点中实现其算法,且不会对功耗、面积或者密度产生任何影响,也不会损失定点特性或功能。用户可以使用Altera的FPGA和SoC来满足大计算量应用需求,例如应用在高性能计算(HPC)、雷达、科学和医疗成像等领域。

精度可调DSP体系结构

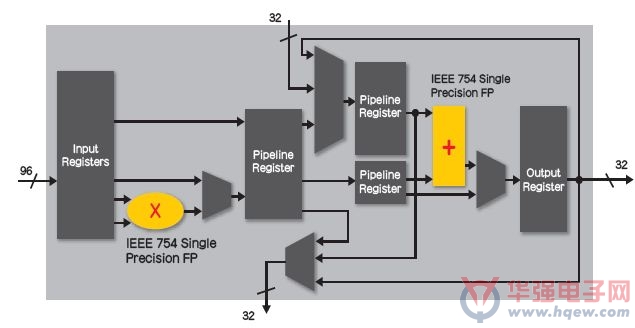

“出色的性能归功于我们创新的精度可调DSP体系结构(图)。”Altera公司首席DSP产品规划经理Michael Parker表示,“该技术在每一DSP模块中包含了一个高精度加法器和单精度乘法器。这些硬核DSP模块中内置了数千个浮点运算器,在20nm系列中,Arria 10 FPGA性能从140 GigaFLOPS(GFLOPS)提升至1.5 TeraFLOPS(TFLOPS);Altera的14nm Stratix 10 FPGA系列将使用相同的体系结构,性能扩展到10 TFLOPS。这是单个器件有史以来最高的性能指标。”

图:具有硬核浮点DSP模块的首款FPGA

该浮点计算单元与现有精度可调定点模式实现了无缝集成。设计人员可以在其设计中使用所有定点DSP处理特性,还可以根据需要将全部设计或者部分设计更新到单精度浮点。IEEE 754浮点所有复数都位于DSP模块的硬核逻辑中,不占用可编程逻辑,即使是100%使用了DSP模块,浮点也支持定点设计中相似的时钟速率。

大幅缩短开发时间

Michael Parker称,自然支持浮点功能对于设计人员在FPGA中实现复杂的高性能算法非常重要。构建系统之前,在浮点中完成所有算法开发和仿真。完成算法后,通常还需要6~12个月的时间在定点实现中进行分析、转换并验证浮点算法。这一过程需要克服以下三个问题:(1)必须手动将浮点设计转换为定点,这需要工程师非常有经验,而且其实现的精度没有仿真高;(2)如果以后对算法进行任何修改,还需要再次进行手动转换,而且优化系统中定点算法的任何步骤都不会反映在仿真中;(3)如果系统集成和测试过程中出现问题,要隔离问题会非常困难。

使用Altera浮点FPGA能够帮助设计人员克服上述问题,它们可以将DSP设计直接转译成浮点硬件,而不是转换为定点,从而大幅缩短了时序收敛和验证时间。相比之前的系列,硬核浮点DSP模块能够缩短近12个月的开发时间。

将与GPGPU展开竞争

据Altera方面透露,与Altera浮点FPGA竞争的并非FPGA,而是GPGPU(General Purpose GPU,即通用图形处理单元,它不是简单的图形引擎,而是通用计算加速器)。Michael Parker表示,这是因为其他FPGA供应商提供的“软核”浮点使用逻辑来实现复数浮点电路的效率不高,还不具竞争力。

FPGA和GPGPU都可以使用OpenCL进行设计,但它们在算法实现上有很大的不同。GPGPU使用并行处理器体系结构,并行运行数千个浮点乘加小单元。算法被分成数万个线程,数据准备好后,映射到计算单元中。

Altera浮点FPGA在高性能计算方面具有突出优势。首先,由于其流水线逻辑体系结构,数据流的处理延时要比GPGPU低得多;其次,FPGA的GFLOPS/W性能要优于GPGPU,这也意味着对于所要求的功率预算,FPGA完成的计算量一般要多于GPGPU;第三,FPGA具有很好的通用性和广泛的连通性,能够直接放在数据通路中处理通过的数据。Altera还专门增加了数据流至其OpenCL工具的选项,以符合OpenCL供应商的扩展要求。

Altera公司软件和DSP产品市场经理Albert Chang介绍,2014年下半年,Altera将提供面向Arria 10器件中硬核浮点DSP模块的浮点设计流程,包括演示和基准测试。在此之前,用户可以采用Arria 10 FPGA开始设计,使用软件浮点技术来实现浮点功能,在得到设计流程支持后,软件工具会自动(一次重新编译)将浮点算法无缝映射到硬核浮点运算中,而不必使用软核逻辑。

关注电子行业精彩资讯,关注华强资讯官方微信,精华内容抢鲜读,还有机会获赠全年杂志。

关注方法:添加好友→搜索“华强微电子”→关注

或微信“扫一扫”二维码

- •芯动科技:借力兼容生态,细分领域下国产GPU的破局之道2022-04-01

- •GPGPU国产替代:中国芯片产业的空白地带2020-08-07

- •采用达芬奇技术搭建视频应用系统实现数字视频创新2019-01-23

- •奥维视讯发布36核多DSP并行计算开发平台2019-01-22

- •DSP与蓝牙模块USB口通信模块设计2019-01-18

- •基于DSP嵌入式技术的智能刹车控制系统电路设计2019-01-18

- •汽车内部噪声智能控制系统电路模块设计2019-01-18

- •基于DSP的视频监控系统硬件电路设计2019-01-18

- •基于DSP的智能视频监控图像处理电路模块设计2019-01-18

- •基于DSP+FPGA多视频监控的采集电路模块2019-01-18