超高集成度FPGA方案加速移动终端“杀手级”功能定制

来源:华强电子网 作者:于宏达 时间:2014-07-21 09:02

不同于其他FPGA厂商重点开发尺寸巨大、运算极快和功耗惊人的芯片,莱迪思对消费类移动电子市场情有独钟,并由此入手,开发出具有差异化的方案和FPGA产品,专注于为业界提供小尺寸、低功耗、低成本的FPGA产品,使用标准平台进行灵活、快速的定制,加快产品上市时间,并以此抢占先机。

自2012年莱迪思推出iCE40 FPGA以来,该系列已出货数亿片,通过将新功能添加到原有设计,作用于简单功能、协处理和加速处理的可编程ASSP,并搭配MachXO3来进行接口桥接和I/O扩展, 尽量减少处理器唤醒,从而为智能手机、平板电脑、可穿戴设备以及其他移动应用带来高效节能的定制化方案。

据莱迪思南中国区技术经理黄晓鹏介绍,近日新推出的iCE40 Ultra系列,相比以前的器件,功耗降低高达75%。相比竞争对手的解决方案,在提供5倍更多功能的同时减小了30%的尺寸,为开发者们实现了更紧凑的设计布局和更长的电池寿命。并独家集成了红外遥控、条形码、触控、用户识别、计步器等新兴功能以及可供定制的极大灵活性,使消费类移动电子设备制造商能够快速实现体现产品差异化的“杀手级”功能。

莱迪思南中国区技术经理黄晓鹏

莱迪思亚洲区高级销售总监梁成志

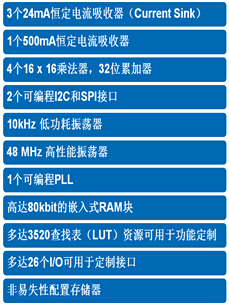

超高度集成是iCE40 Ultra拥有的特性,大量IP硬核可以实现快速升级和创新。例如,iCE40 Ultra中集成了SPI、I2C和可编程I/O,振荡器和PLL,RAM、DSP和可编程架构,非易失性配置存储器等,可以满足设计者旧接口和协议与新硬件和标准间的桥接,实现时序和协议控制,运行状态机和处理算法,瞬时启动无需唤醒处理器等需求。

iCE40 Ultra集成的IP硬核

莱迪思亚洲区高级销售总监梁成志进一步补充说,iCE40 Ultra集成了所有前几代iCE40器件中的IP硬核,同时增加乘法器和累加器来完成基本的DSP运算。许多基于传感器的新应用需监测、验证、处理多路数据流,然后再交给应用处理器进行处理,乘法器和累加器块用于完成如傅利叶变换或卡尔曼滤波等实时复杂运算,用于数据的预处理和滤波,因为它的实时性和低功耗特性能够减少主处理器的工作,并使主处理器尽可能长时间地处于休眠状态。这种类似于ASSP的集成降低了系统功耗并加快了功能实现,因此设计者们可以将更多的时间用在功能定制上。

据悉,iCE40 Ultra产品系列中尺寸最小的器件为1.7mm x 2.1 mm x 0.45 mm的WLCS封装(晶圆级芯片封装),目前市场上没有任何一个解决方案能够在如此小的封装内以如此低的功耗实现这么多的功能以及灵活性。因此该系列非常适合用于通用扩展、非差分低速桥接、电平转换和其他消费电子移动设备的常用功能。

关注电子行业精彩资讯,关注华强资讯官方微信,精华内容抢鲜读,还有机会获赠全年杂志。

关注方法:添加好友→搜索“华强微电子”→关注

或微信“扫一扫”二维码

- •莱迪思将其FPGA拓展至智能和嵌入式视觉系统2020-09-11

- •莱迪思推出全新Certus-NX,重新定义低功耗通用FPGA2020-06-29

- •莱迪思完整解决方案集合 可打造低功耗智能视觉应用2020-05-21

- •莱迪思拓展其模块化视频接口平台(VIP) 以简化嵌入式视觉系统的视频互连设计2018-05-17

- •全新的莱迪思Snap模块可帮助厂商快速构建 替代USB连接器的12 Gbps无线解决方案2018-02-26

- •美媒:中国2017年收购美技术企业规模总量大跌87%2018-01-08

- •莱迪思推出面向千兆级无线基础设施应用的GigaRay 60 GHz模块2017-12-06

- •莱迪思推出HDMI 2.1增强音频回传通道(eARC)解决方案2017-12-05

- •莱迪思推出HDMI 2.1增强音频回传通道(eARC)解决方案2017-11-30

- •莱迪思MachXO3控制PLD器件,增强嵌入式I/O扩展和电路板级管理功能2017-11-07