基于FPGA的高速FIFO电路设计

来源:慧聪网 作者:—— 时间:2010-05-27 09:42

前言

在大容量高速采集系统项目的开发过程中,FPGA作为可编程逻辑器件,设计灵活、可操作性强,是高速数字电路设计的核心器件。由于FPGA内嵌存储器的容量有限,通常不能够满足实际设计电路的需求,需要外接SRAM、SDRAM、磁盘阵列等大容量存储设备。本文主要介绍高速FIFO电路在数据采集系统中的应用,相关电路主要有高速A/D转换器、FPGA、SDRAM存储器等。图1为本方案的结构框图。A/D输出的数据流速度快,经过FPGA降速后,位数宽,速度仍然很高,不能直接存储到外部存储器。在设计时,要经过FIFO缓存,然后才能存储到外部存储器。本设计的FIFO容量小、功能强,充分利用了FPGA内部FIFO电路的特点,结合实际电路,优化了整个电路模型的设计。

异步FIFO生成

FIFO占用的内存资源为FPGA内嵌的block RAM,由Xilinx公司提供的ISE开发平台自动生成。读写时钟有通用时钟和独立时钟可选,我们采用独立时钟,rd_clk和wr_clk独立,为了保证在高速采集时数据不丢失,rd_clk频率不低于wr_clk。FIFO读模式采用标准FIFO,每次启动采集时都要对FIFO进行复位,为异步复位,初始化内部指针和输出寄存器。在FIFO生成过程中,我们启用almost_full 和almost_empty选项,以及prog_full 和prog_empty选项,prog_full和prog_empty要进行参数设置,具体设置参数如图2所示。

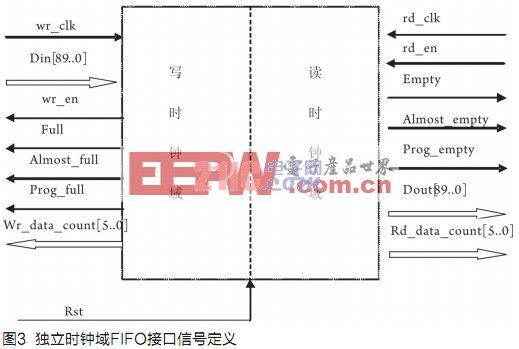

FIFO接口信号定义

根据FIFO的生成过程,在图3中给出了读写时钟域的信号定义,所有的在写时钟域的输入信号都必须经过写时钟同步,所有的在读时钟域的输入信号都要经过读时钟同步。信号经过时钟同步后,可以确保在读写过程中不会出现亚稳态,导致读写操作出现错误。

下面对读写时钟域定义信号给予说明:

rst:复位信号,高有效,异步复位,每次启动采集都要首先对FIFO进行复位;

wr_clk:写时钟;

wr_en:与写时钟同步;

din:输入数据总线;

rd_clk:读时钟;

dout:输出数据总线;

full:FIFO全满标志;

empty:FIFO全空标志;

almost_full:高有效,如果为高电平,在写一个数据FIFO将全满;

almost_empty:高有效,如果为高电平,在读一个数据FIFO将全空;

prog_full:可编程满标志,根据需要,可以设定FIFO内部有多少数据,该标志信号有效;

prog_empty:可编程空标志,根据需要,可以设定FIFO内部有多少数据,该标志信号有效;

wr_data_count:说明FIFO内部已经写了多少数据;

rd_data_count:说明FIFO内部有多少数据可以读。