基于16位8通道DAS AD7606的系统布局考虑

来源:华强电子网 作者:ADI 时间:2010-12-17 10:03

电路功能与优势

在电力线路测量和保护系统中,需要对多相输配电网络的大量电流和电压通道进行同步采样。这些应用中,通道数量从6个到64个以上不等。AD76068通道数据采集系统(DAS)集成16位双极性同步采样SAR ADC和片内过压保护功能,可大大简化信号调理电路,并减少器件数量、电路板面积和测量保护板的成本。高集成度使得每个AD7606只需9个低值陶瓷去耦电容就能工作。 在测量和保护系统中,为了保持多相电力线网络的电流和电压通道之间的相位信息,必须具备同步采样能力。AD7606具有宽动态范围,是捕获欠压/欠流和过压/过流状况的理想器件。输入电压范围可以通过引脚编程设置为±5 V或±10 V。 此电路笔记详细介绍针对采用多个AD7606器件应用而推荐的印刷电路板(PCB)布局。该布局在通道间匹配和器件间匹配方面进行了优化,有助于简化高通道数系统的校准程序。当通道间匹配非常重要时,此电路可以使用2.5 V内部基准电压源AD7606;而对于要求出色绝对精度的高通道数应用,此电路可以使用外部精密基准电压源ADR421,它具有高精度(B级:最大值±1 mV)、低漂移(B级:最大值3 ppm/°C)、低噪声(典型值1.75 μV p-p,0.1 Hz至10 Hz)等特性。低噪声及出色的稳定性和精度特性使得ADR421非常适合高精度转换应用。这两个器件相结合,能够实现业界前所未有的集成度、通道密度和精度。 电路描述 AD7606是一款集成式8通道数据采集系统,片内集成输入放大器、过压保护电路、二阶模拟抗混叠滤波器、模拟多路复用器、16位200 kSPS SAR ADC和一个数字滤波器。图1所示电路包括两个AD7606器件,可以配置为使用2.5 V内部基准电压源或2.5 V外部基准电压源ADR421。如果REF SELECT引脚接逻辑高电平,则选择内部基准电压源。如果REF SELECT引脚接逻辑低电平,则选择外部基准电压源。 电源要求如下:AVCC = 5 V, VDRIVE = 2.3 V至5 V(取决于外部逻辑接口要求)。 本电路笔记描述一个评估板的布局和性能,其中内置两个AD7606,构成一个16通道数据采集系统。为实现良好的通道间匹配和器件间匹配,模拟输入通道和器件去耦的对称布局非常重要。所示数据支持利用图1所示16通道ADC实现的匹配性能。

图1. 采用两个AD7606 8通道DAS的16通道、16位数据采集系统

16通道DAS的双路AD7606板布局

在内置多个AD7606器件的系统中,为确保器件之间的性能匹配良好,这些器件必须采用对称布局。图2显示采用两个AD7606器件的布局。

图2. 采用两个AD7606的16通道DAS的PCB布局

AVCC电压平面沿两个器件的右侧布设,VDRIVE 电源走线沿两个AD7606器件的左侧布设。基准电压芯片ADR421位于两个AD7606器件之间,基准电压走线向上布设到U2的引脚42,向下布设到U1的引脚42。使用实心接地层。这些对称布局原则适用于含有两个以上AD7606器件的系统。AD7606器件可以沿南北方向放置,基准电压位于器件的中间,基准电压走线则沿南北方向布设,类似于图2。 良好的去耦也很重要,以便降低AD7606的电源阻抗,及其电源尖峰幅度。去耦电容应靠近(理想情况是紧靠)这些引脚及其对应接地引脚放置。 REFIN/REFOUT引脚和REFCAPA、REFCAPB引脚的去耦电容是攸关性能的重要电容,应尽可能靠近相应的AD7606引脚。可能的话,应将这些电容放在电路板上与AD7606器件相同的一侧。图3显示AD7606电路板顶层的建议去耦配置。所示的四个陶瓷电容是REFIN/REFOUT引脚、REGCAP引脚、REFCAPA引脚和REFCAPB引脚的去耦电容。这些电容沿南北方向放置,以便尽可能靠近相应的引脚。

图3. 顶层去耦,显示了两个REFCAPA引脚、REFIN/REFOUT引脚和REFCAPA/B引脚的去耦电容

图4显示底层去耦配置,它用于四个AVCC引脚和VDRIVE引脚的去耦。使用多个过孔将引脚与其相应的去耦电容相连。AD7606器件周围去耦电容的对称布局有利于器件间的性能匹配。多个过孔用来将电容焊盘和引脚焊盘接地及接到电压平面和基准电压走线。

图4. 底层去耦,显示了四个AVCC引脚和VDRIVE引脚的去耦电容

16通道系统的通道间匹配在高通道数系统中,良好的通道间和器件间性能匹配可以大大简化校准程序。AD7606器件、模拟输入通道和去耦电容的对称布局有助于多个器件之间的性能匹配。使用公共系统基准电压将能进一步增强系统的匹配性能。图5显示所有输入接地时,用于测量板上16个通道之间性能匹配的电路配置。还有最多7个码的分布直方图,各通道直方图的中心为码0,如图6所示。

图5. 用于测试16通道系统通道间匹配的电路示意图,该系统采用两个AD7606和外部基准电压源ADR421,所有输入接地

图6. 图5所示电路的直方图,显示了使用外部基准电压源ADR421的16通道系统的通道间匹配性能

AD7606内部基准电压源用作系统基准电压源AD7606内置一个2.5 V基准电压源,经过内部放大,它可以为AD7606 ADC提供约4.5 V的缓冲基准电压。在通道间和器件间匹配性能至关重要的高通道数应用中,可以用一个AD7606的内部基准电压源为另一个AD7606器件提供基准电压。在此配置中,U1配置为在内部基准电压下工作,如图7所示。

图7. 用于测试一个AD7606通道间匹配的电路示意图,使用U1内部基准电压源

AD7606 U2器件可配置为在外部基准电压源模式下工作。U1 REFIN/RFOUT引脚提供的2.5 V基准电压路由至U2的REFIN/REFOUT引脚。一个10 μF去耦电容位于AD7606器件的REFIN/REFOUT引脚。在AD7606 U1和U2上,REFCAPA和REFCAPB引脚短接在一起,并通过一个10 μF陶瓷电容去耦至GND。 两个AD7606器件均以200 kSPS的采样速率工作,一个7.5 V直流信号施加于U1的V1和V2,如图7所示。码的直方图如图8所示。在同一器件的通道之间,平均输出码相差1.2个码。板上的所有16个通道以200 kSPS速率进行转换。

图8. 图7所示电路的直方图

7.5 V信号施加于U1的V1和U2的V1,板上的所有16个通道以200 kSPS速率工作,如图9的配置电路示意图所示。码的直方图如图10所示。在不同器件的V1通道之间,平均输出码相差1.4个码。 图9. 用于测试两个AD7606之间器件间匹配的电路示意图,U1内部基准电压源用作系统基准电压源

图9. 用于测试两个AD7606之间器件间匹配的电路示意图,U1内部基准电压源用作系统基准电压源

图10. 图9所示电路的直方图

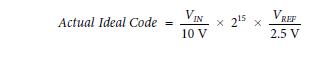

将一个AD7606的内部基准电压源用作系统基准电压源时,以上直方图显示,一个AD7606器件的通道之间以及多个器件的通道之间都具有非常好的匹配性能。 绝对精度除了通道间匹配和器件间匹配外,如果ADC转换结果的绝对精度也非常重要,则应使用外部小容差、低漂移基准电压源作为系统基准电压源。在该电路中,ADR421 2.5 V基准电压源用作系统基准电压源。 施加于AD7606器件的基准电压会影响ADC输出码:

实际理想码的值会因温度而不同,具体取决于系统基准电压源的温度系数特性。在绝对精度非常重要的应用中,或者在希望避免通过复杂的温度校准程序实现绝对精度和通道匹配的应用中,应当使用ADR421等小容差、低漂移2.5 V基准电压源作为AD7606器件的系统基准电压源。

7.5 V直流电压施加于U1的输入(V1和V2),如图11的电路所示,并使用外部基准电压源。U1的两个通道的码直方图如图12所示。两个通道的码直方图平均值相差0.9 LSB。

图11. 用于测试一个AD7607通道间匹配的电路示意图,使用外部基准电压源

图12. 图11所示电路的直方图

在用于测试器件间匹配的图13所示电路中,7.5 V直流信号施加于U1和U2 AD7606器件的V1通道,并使用外部基准电压源。两个AD7606器件的两个V1通道的码直方图如图14所示。板上的所有16个通道以200 kSPS吞吐速率工作。U1和U2的V1通道之间的码直方图平均值相差0.6 LSB。

图13. 用于测试两个AD7606器件间匹配的电路示意图,使用外部基准电压源

图14. 图13所示电路的直方图

以上直方图显示,采用ADR421外部系统基准电压源时,一个AD7606器件的直方图平均值间匹配和多个AD7606器件的直方图平均值间匹配均小于1 LSB。 结论本布局能够确保通过一个AD7606实现通道间良好匹配性能,并且同一PC板上的多个AD7606之间也具有良好的器件间匹配性能。AD7606器件的对称布局,特别是去耦电容将有助于实现良好的通道间匹配和器件间匹配。在高通道数系统中,良好的通道间和器件间性能匹配意味着校准程序得以简化。