LED显示屏驱动设计原理及发展趋势

来源:华强LED网 作者:—— 时间:2010-12-30 14:28

㈡ 驱动芯片时序

CYT62726内部是16位移位寄存器,多颗CYT62726串行数据移位,每个时钟周期CLK移送1位数据SDI,串行数据输入驱动器开/关控制。施密特缓冲输入。当其中数据“1”被写入到SDI的开关控制移位寄存器/时CLK的上升沿。

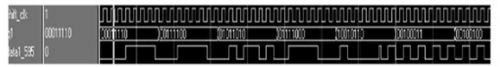

灰度控制模块仿真波形图

CLK 串行数据移位时钟。施密特缓冲输入,所有的数据/关控制的转变移位是由1位的最高位同步的CLK的上升沿,单路数据移位到SD在同一时间。 CLK的上升沿输入获准后,持续100ns的上升沿。

LE 边沿触发锁存器。施密特缓冲输入。当前对应移位寄存器中数据,在此上升沿数据被锁存。

移位锁存仿真波形图

OE 所有输出空白。施密特缓冲输入。当OE是低电平时,所有恒流输出(OUT0?15)被执行。当OE= 1,所有恒流输出控制的开关在数据控制数据/锁存状态。OE决定执行数据长度时间。

这种时序传输方式是,沿用74HC595通用逻辑数据传输方式,在LED屏幕上已经使用了十多年历史,显得古老而落伍。LED屏幕亟待新的数据传输格式,简化的、高效的传输方式,从而减低设计复杂度,降低设计成本和提高屏幕可靠性。

数据和时钟需要协调一致,可是在线路设计中,数据采用串行传输,而时钟则是并行传输,势必数据延时会造成输出错位。这是4线传输格式最大的缺点,数据和时钟不能很好的同步,级联性较差,控制器成本高。落伍的数据传输格式,控制器产生灰度等级,屏幕刷新率低,传输数据量大,是LED屏幕目前发展瓶颈。

上一篇:设计创新调动LED市场潜能

- •艾笛森力推全方位LED照明整合服务方案2012-12-13

- •BCD推出最高功率因子LED驱动解决方案2012-09-14

- •DAS为LED工业开发创新型废气解决方案2012-09-14

- •BCD Semi推出高功率因子LED驱动电源解决方案2012-09-13

- •红外LED在安防监控摄像机中运用的误区2012-08-27

- •估算LED寿命 LM-80与TM-21谁更准确2012-08-15

- •浅谈LED显示屏之LED驱动电源隔离之间的差异2012-08-13

- •飞兆半导体解决方案加速LED照明节能进程2012-08-13

- •欧司朗:高显指高光效混色LED方案2012-08-10

- •LED芯片及封装专利布局和卡位2012-08-09