莱迪思宣布首个符合PCI Express 2.0规范的低成本FPGA

来源:华强电子网 作者:—— 时间:2011-07-06 11:02

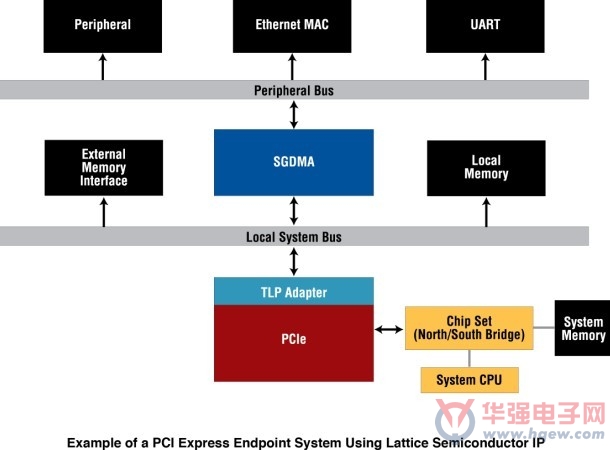

莱迪思半导体公司今日宣布LatticeECP3TMFPGA系列符合PCI Express 2.0在2.5Gbps的规范。针对最近PCI – SIG研讨会上涉及的1-通道和 4-通道配置,LatticeECP3 FPGA和其PCI Express(PCIe)IP核通过了符合PCI - SIGPCIe 2.0规范和互操作性的测试,确保莱迪思的解决方案与现有的支持系统的PCIe 2.0具有互操作性。实现这一重要行业事件使得2.5Gbps PCIe v2.0系统具有更高的可靠性且降低了成本和功耗,适用于通信、多媒体、服务器和移动平台,莱迪思及其IP合作伙伴增加了更加广泛的设计解决方案,支持被广泛采用的串行互连标准。

在PCIe 2.0规范允许工作在一个较低的速度(2.5Gbps),但环路带宽的特点是不同的,比PCIe 1.1版更加严格。莱迪思的解决方案使不需要PCIe链路工作在5Gbps,但关注符合有关PCIe 2.0规范的用户在符合PCIe 2.0规范的系统中使用低成本FPGA。

此外,针对莱迪思的PCI Express x1和x4的IP核,莱迪思与Trellisys有限公司提供了强大的和具有成本效益的PCIe总线功能模型(BFM)。同时有一些针对PCI Express的第三方验证的核可用,这些通常是针对ASIC /定制逻辑,在FPGA开发过程中,验证IP的成本往往使人望而却步。Trellisys的PCIe BFM集中在事务层,因为通常在那里实现用户的应用逻辑。这种方法假定物理和数据链路层完全压缩在莱迪思的PCIe IP核中,已经由莱迪思验证。

“Trellisys的PCI Express BFM使验证投入符合FPGA开发流程,同时仍然保持有效的验证概念,” Trellisys的总监Charles Gardiner说道。 “与PCI Express 1.1相比,由于PCI Express 2.0有更严格的测试要求,对PCI Express2.0规范的成功测试为与其他符合PCI Express2.0规范的器件一起工作提供了更稳定的运作。”

Trellisys的PCIe BFM支持Verilog和VHDL,并已在Aldec公司的Active- HDL及Riviera - PRO仿真器上进行了验证。提供预编译的代码,为用户提供了基于先进验证套件的强大的程序库。设计人员可以立即用Lattice Diamond? 1.2或更高版本的设计工具套件中的IPexpress?工具,开始评估和设计采用LatticeECP3莱迪思的符合PCI Express 2.0规范的系统。该IPexpress工具提供了PCIe核,参考设计和所有的脚本,BFM和模拟模型需要精简集成至用户设计。

“我们与Trellisys的关系增强了我们自己的技能,并重申我们的一贯致力于LatticeECP3 PCI Express IP产品组合的承诺,”莱迪思器件和解决方案的市场总监Shakeel Peera说道。 “这种合作提供了验证的IP,使用户减少设计的复杂性,针对他们的PCI Express设计缩短了产品的上市时间。”

- •莱迪思将其FPGA拓展至智能和嵌入式视觉系统2020-09-11

- •莱迪思推出全新Certus-NX,重新定义低功耗通用FPGA2020-06-29

- •莱迪思完整解决方案集合 可打造低功耗智能视觉应用2020-05-21

- •莱迪思拓展其模块化视频接口平台(VIP) 以简化嵌入式视觉系统的视频互连设计2018-05-17

- •全新的莱迪思Snap模块可帮助厂商快速构建 替代USB连接器的12 Gbps无线解决方案2018-02-26

- •美媒:中国2017年收购美技术企业规模总量大跌87%2018-01-08

- •莱迪思推出面向千兆级无线基础设施应用的GigaRay 60 GHz模块2017-12-06

- •莱迪思推出HDMI 2.1增强音频回传通道(eARC)解决方案2017-12-05

- •莱迪思推出HDMI 2.1增强音频回传通道(eARC)解决方案2017-11-30

- •莱迪思MachXO3控制PLD器件,增强嵌入式I/O扩展和电路板级管理功能2017-11-07