初心不改,芯耀辉高速接口IP助攻芯片设计制胜USB新标准

引言:作为高速接口IP新锐企业,芯耀辉对USB接口的发展历史、未来趋势和设计挑战等有深刻洞察,并基于多年设计积累和优秀架构提供灵活易用的完整解决方案,帮助设计人员应对挑战,实现设计目标。

我们对速度的不懈追求,使得终端产品升级换代的节奏越来越快。如何面向未来需求加快产品上市?如何应对高速接口设计及测试挑战?近日,由全球测试测量行业领先者安立公司、泰克公司及GRL,共同举办的2021高速接口联合测试论坛,针对行业热点关切,特邀芯片设计、IP及设备相关领导厂商进行深入探讨。

作为高速接口IP新锐企业,芯耀辉科技受邀出席本次盛会。芯耀辉科技技术支持总监刘好朋以“消费类电子接口发展展望——USB会一统天下吗?”为主题进行精彩分享,并深入介绍了芯耀辉USB PHY IP方案,现场反应热烈。

图:芯耀辉科技技术支持总监刘好朋

发展历史丨30年风云,USB王者之气渐显

USB全称是Universal Serial Bus,名称体现了其通用性强、传输率高、兼容性好和即插即用的初心。迄今,USB接口标准已经历了3个阶段。第一阶段始于1995年,为解决接口通用性问题,第一代USB标准问世,传输速度仅为1.5Mbps,业内反响平平。第二阶段自2000年始,USB 2.0传输速度达到480Mbps,被广泛应用于各种数据传输应用。但在随后5年多间,USB标准并无新的亮点。

新的突破在第三阶段,以2008年发布USB 3.0、传输速度突破至5Gbps为标志。随后,2013年传输速度为10Gbps的USB3.1,2017年传输速度达20Gbps的USB3.2陆续发布。2019年发布的最新的USB4,最高速度可达40Gbps,终端产品于2020年底陆续面市,特别是英特尔酷睿11代产品集成了支持USB4的Thunderbolt 4,被业内视为USB4标准开始普及的标志性事件。

图:USB标准发展史

未来趋势丨USB技术演进瞄准高速、兼容

多年来,USB接口标准不断更新升级,得益于强大的兼容性,不同代际共存于市的情况很普遍。刘好朋从USB应用市场采纳角度分析,呈现两种趋势:一个是传统应用中,新标准普及节奏快慢不一;另一个是新兴应用中,新标准起驱动作用。

举例而言,游戏、VR/AR等设备对新的USB标准采纳最为保守。虽然需求量很大,但它们更渴盼统一接口,整合所有电源线、控制线、数据线、音视频线等。USB4等新一代USB标准符合以上的需求,更适合这个场景,可支持4K、8K甚至未来的10K视频传输,再加持低延时、可变刷新率等先进特性给用户带来更好的使用体验,将加快该类应用对USB新标准的采纳进程。

他还提到应用市场的发展,促使USB接口技术演进呈现以下趋势:持续挑战更高传输速度;不断兼容多种协议等。

预计2025年前后,USB接口的传输速度有望达到近80Gbps,继续保持相对Thunderbolt的竞争力。同时, Type-C作为大一统的接口形态,其机械特性和电气特性会有进一步优化设计;而连接线缆可能全部被主动式线缆取代,来适配长度要求。

USB也将继续保持对多协议的兼容,包括对不同代际的USB标准,如USB 3.1、USB 3.2和USB4等,以及快充标准USB PD,还有DisplayPort、PCIe、Thunderbolt,未来甚至 HDMI 和 以太网等都有可能将纳入USB接口支持范围,成为名副其实“一统天下”的王者。

挑战及应对丨芯耀辉先进USB IP,破解高速接口设计挑战三大难

USB市场空间可观,但产品快速落地和迭代,给芯片设计和测试提出了更多挑战:传输速度极高,接口协议极多,快充协议极多,协议升级加快。作为高速接口IP供应商,芯耀辉对此有如下洞察,并基于USB PHY IP多年设计积累和优秀架构提供灵活易用的完整解决方案。

挑战一:需要适配各种复杂应用场景。

如图,为支持不同的编码,包括8/10bit,128/132bit,还有可选的64/66bit;不同的协议,USB、DP,以及可选的Thunderbolt、PCIe等,以及繁多的传输速率和协议电气特性等。IP设计上需要通盘考虑、逐个优化。

图:USB PHY IP设计挑战——适配复杂应用场景

挑战二:更加严苛的信道插损预算。

USB3.1 Gen1 5Gbps的信道插损根据DFP和UFP不同、接口类型不同,预算不尽相同,连接线缆的要求也不相同。而USB3.1 Gen2 10Gbp,统一了DFP和UFP的预算,和接口类型、线缆无关。但这其实变相提升了对封装、PCB、线缆的设计要求,更是提高了PHY IP的设计难度。因为一颗芯片必须要适配多种不同应用场景,对IP设计、整个芯片系统设计和测试提出了更高的要求。

图:USB PHY IP设计挑战——严苛的信道插损预算

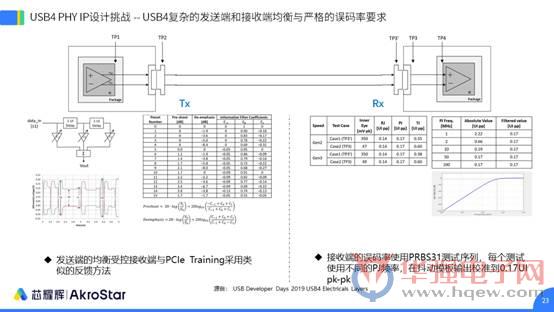

挑战三:USB4复杂的发送端和接收端均衡与严格的误码率要求。

USB4链路训练采用和PCIe Training类似反馈方法,发送端在发送训练序列的同时,将自身接收端对于对接发送端的FFE请求反馈,在预设值中找到适应的最优均衡值。USB4要支持多达16个预设值的快速遍历。接收端要适应不同频率的周期抖动,每一个周期抖动都要通过PRBS31的低误码率测试,协议要求误码率1e-12,为了尽可能增加系统设计的裕量,通常IP在设计中会把目标误码率降低到1e-13,甚至更低水平。

图:USB4 PHY IP设计挑战 -- USB4复杂的发送端和接收端均衡与严格的误码率要求

芯耀辉先进USB PHY IP解决方案

针对这些设计挑战,芯耀辉提供极具灵活性的完整解决方案适配各种应用场景并向下兼容,包括USB4和USB 3.1 Type-C解决方案。

芯耀辉USB 3.1Type-C解决方案,具有领先的架构和设计,已在大量移动应用中得到验证。针对所有需要Type-C的应用,USB速率达到10Gbps,DP HBR3速率达到8.1Gbps,并具有HDCP 2.3 内容保护。

芯耀辉USB4 IP解决方案,支持USB4规范中所有功能;通过Type-C连接,支持USB4、DisplayPort、PCIe和Thunderbolt3;新的Router IP可使USB、PCIe和DisplayPort在优化带宽的同时传输数据流;高达40Gbps(或20Gbps)的吞吐量,可用于高性能AI、高速存储、PC、笔记本、手机和平板SoC等设计。

图:芯耀辉USB4和USB 3.1Type-C完整解决方案优势

在演讲的最后,刘好朋向到场嘉宾介绍称,芯耀辉科技是一家拥有行业“梦之队”的初创IP公司,致力于通过先进半导体IP研发服务,赋能客户的芯片设计和系统应用。芯耀辉科技创始团队是来自IP设计、芯片设计、软件等行业顶尖人才,曾与国内外具备量产能力的顶尖和主流客户一同打造全球领先产品,并长期共同迭代,有着超过20年的深厚积累,深谙芯片设计的痛点,还可提供一系列定制的IP升级服务。芯耀辉科技愿意与更广泛的客户携手合作,助力芯片设计厂商取得更大成功。

- •活动回顾丨 AI 赋能消费电子创新应用论坛圆满落幕!2026-04-14

- •Vishay荣获欧摩威汽车系统(长春)有限公司2025年供应链卓越奖2026-04-14

- •AMD 正面挑战 NVIDIA 霸权!2026-04-14

- •Intel股价暴涨43%:资本市场情绪正在发生反转2026-04-14

- •eFuse如何助力汽车电气化2026-04-14

- •晶存科技亮相2026半导体产业发展趋势大会并获双项荣誉2026-04-14

- •赋能智能车与机器人技术转型:大联大世平集团携手AutoSys举办线上研讨会2026-04-14

- •Vishay双路Wilkinson功率分配器/合成器在高频连接应用中提高效率并节省空间2026-04-14

- •泰瑞达推出Photon 100全面型自动测试平台,加速大规模硅光子和共封装光学量产2026-04-14

- •思特威推出全新升级1.3MP高性能车规级CMOS图像传感器2026-04-14