矽中介层制造商渐增 2.5D芯片成本将下滑

来源:华强电子网 作者:—— 时间:2012-10-23 10:04

【摘要】2.5D晶片生产成本不再居高不下。FPGA业者赛灵思(Xilinx)以台积电矽中介层(Silicon

Interposer)技术所生产的2.5D异质整合晶片Virtex-7,已引起市场高度关注,并吸引其他晶圆代工厂开始加入矽中介层晶圆生产行列,可望加速矽中介层晶圆制造成本下降,并助长2.5D晶片发展。

赛灵思Virtex-7SSI技术

赛灵思(Xilinx)以堆叠式矽晶封装互连技术(Stacked Silicon Interconnect Technology, SSIT)为基础,推出现场可程式逻辑闸阵列(FPGA)系列--Virtex-7 2000。过去一年半,赛灵思不断主打其各种不同FPGA处理器频宽及低耗电量的效能表现。

赛灵思(Xilinx)以堆叠式矽晶封装互连技术(Stacked Silicon Interconnect Technology, SSIT)为基础,推出现场可程式逻辑闸阵列(FPGA)系列--Virtex-7 2000。过去一年半,赛灵思不断主打其各种不同FPGA处理器频宽及低耗电量的效能表现。

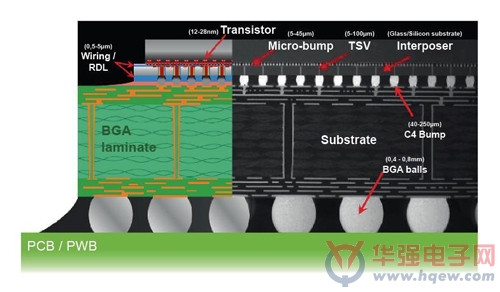

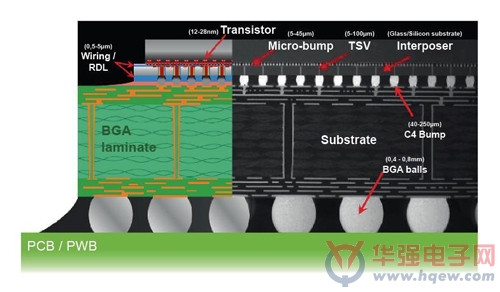

Virtex-7 2000T模组封装外表大小约为45×45平方毫米(mm2)的一千两百球栅阵列封装(Ball Grid Array,

BGA)。一个以65奈米(nm)互补式金属氧化物半导体(CMOS)设计规则构想出的三维(3D)被动矽中介层,以覆晶(Flip-chip)技术放置在有机BGA基板上,再以热回流焊接(Thermal

Solder Reflow)固定。

这个3D中介层共包含四层厚达100微米(μm)的平面金属层,三层为有颗粒花纹的铜及一层铝,以铜完全覆盖直径约10~12微米的导通孔,预估中介层的大小大概接近10平方公分。在中介层之上是俗称为“切片(Slices)”的28奈米CMOS,包含可替换的数位讯号处理器(DSP)、记忆体、可程式逻辑列,以及串列器/解串列器(

SerDes)介面区块,预估每片的表面区域大概是200平方毫米,为异质整合的形式,意即将各种不同功能的积体电路(IC)组装于同一个基板上。

Virtex-7

2000T采用的是矽基板,以覆晶技术将IC与中介层贴合,在两个连续凸块间,以最小为45毫米的高度覆合铜锡合金微凸块,再以高度精密的热压焊进行焊接制程。如同其他较大型的晶片一样,Virtex-7

2000也须在封装的最上方覆上散热片(图1)。

图1 Virtex-7 2000T跨部分及整个模组的概要图示

中介层生产成本居高不下

Yole

Developpement预测此一中介层的量产良率达95%,而组装良率高达99%;通常组装良率都比较高,但Yole分析良率时也已将整个模组的复杂性及五个高精密覆晶的焊接步骤列入考量。Yole预测生产此一矽中介层的代工厂是已折旧的CMOS

65奈米制程工厂,也就是台积电七厂。

Yole Developpement不认为台积电在2012年会生产超过一万片直径300毫米的中介层晶圆,预计矽穿孔(Through Silicon

Via, TSV)相关的制造设备将无法摊销,但重分布层(Redistribution

Layer)则可随着设备的折旧而完成摊提。矽穿孔相关的设备包含通孔蚀刻制程用的深反应离子蚀刻(Deep Reactive Ion Etching,

DRIE)、填满通孔之镀铜制程、晶圆键合与剥离、矽穿孔露出作业之晶圆薄化。

Yole

Developpement以矽穿孔成本计算工具及成本模型来推测矽中介层的生产成本,在2012年平均每片中介层晶圆的总制造成本是683元美元,其中61%是设备成本的摊销,21

%是材料、耗材(气体及化学品)、能源及水的成本,11%为裸晶圆(矽晶圆及焊接载体),5%为产出亏损,以及2%的人力成本。看起来矽穿孔相关的制程步骤占整体制造成本的四分之三,但当未来相关的设备开始折旧后,这些成本的比例也将逐渐下降。

Yole

Developpement预测台积电一开始将会大幅提高中介层晶圆的利润比例(60%),预计2012年底时每片晶圆的价格约为1,700美元,也就是每个中介层单价最高达30美元左右。

上一篇:IC封测产业淡季不淡

相关文章

- •更小、更薄、更轻!兆易创新业界超小尺寸3mm×3mm×0.4mm FO-USON8封装128Mb SPI NOR Flash面世!2023-05-17

- •Vishay推出两款采用SMA(DO-214AC)封装的新型第7代1200 V FRED Pt Hyperfast恢复整流器2023-01-30

- •三星电子成立半导体封装工作小组2022-07-05

- •士兰微:子公司30亿元投资建设汽车级功率模块封装项目2022-06-14

- •日月光凭借先进封装切入美国一流服务器芯片厂商供应链2022-04-27

- •芯片交期再度延长,封装交期延长至50周2022-04-14

- •芯和半导体在DesignCon 2022大会上发布新品Hermes PSI及众多产品升级2022-04-07

- •森阳电子半导体封装项目签约落地四川攀枝花2022-03-23

- •台积电竹南封测厂Q3量产,将进行大规模的3D封装量产计划2022-03-22

- •武汉芯片企业云岭光电国内率先量产5G芯片2022-03-17