矽中介层制造商渐增 2.5D芯片成本将下滑

来源:华强电子网 作者:—— 时间:2012-10-23 10:04

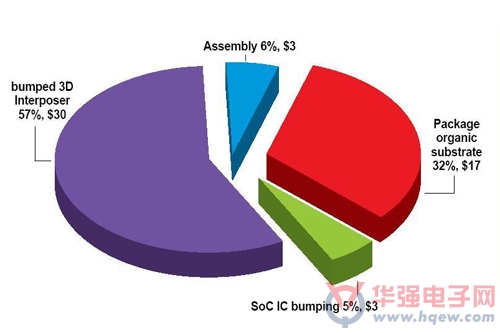

封装基板为4+2+4的覆晶有机BGA嵌入式基板,预测基板业者订定的售价约落在每片17美元,整体组装的成本大约是2美元,且有60%以上会有1

%的组装产出亏损。

Virtex-7模组的CMOS矽区块可能高达125美元,预测用在CMOS晶粒及矽中介层间的非导电性黏着剂(Non-Conductive Paste,

NCP)将构成整体组装成本的四分之一。假设封测代工厂(OSAT)艾克尔(Amkor)的组装及封装服务利润为30%,那么赛灵思就可能必须付出接近3美元的成本于基板/中介层/CMOS晶粒堆的组装,以及额外的3美元成本用于俗称为CMOS

FPGA切片的铜凸块。

若要发展一款FPGA可编程逻辑闸数目与Virtex-7相比拟,但功耗较高、处理频宽较小的新解决方案,至少需要两颗单独晶粒的封装,而这些晶粒可能会比Virtex-7

SSIT解决方案中200平方毫米的FPGA切片大上两倍。

众所皆知,晶粒尺寸越大良率就越糟糕。所以,新的SSIT解决方案一方面使用可能会相当昂贵的矽中介层,另一方面要实现等同闸数的“标准”解决方案又需要两个封装而非一个,再加上CMOS晶圆厂前端制程良率还有问题。因此,整体而言,估计到今年底时,这两种解决方案的成本约不相上下,但Virtex-7

2000 T 的新SSIT解决方案应该会具有较明确的效能优势。

晶圆代工厂分食中介层大饼

2012年台积电开始替赛灵思量产后,预计未来会吸引越来越多晶圆代工业者制造矽中介层晶圆,这将扩大整体经济规模,并摊销矽穿孔相关高昂设备成本,因此Yole

Developpement以台积电的矽中介层的合理成长幅度,推测未来SSIT解决方案的价格下降曲线。

未来台积电的竞争者很可能开始争食中介层这块大饼,将逐渐侵蚀利润比例,图2为上述两个解决方案的预测价格比较,Yole认为未来五年赛灵思的SSIT以矽为主的技术将有大幅降价的潜力,且将远超过标准的单晶粒封装解决方案。

图2 赛灵思SSI解决方案及替代性解决方案预测价格比较

赛灵思的SSIT矽中介层模组看起来不仅仅是有噱头的高效能展示而已,根据Yole

Developpement模拟,该模组高度符合成本效益,而且跟低效能的解决方案相比还相当具有成本竞争力。

目前赛灵思的解决方案单位定价是500美元以上,实际上量产的价格可能落在600至800美元左右,确实相当高阶且昂贵,但姑且不管那些与未来CMOS节点替代性发展的比较,其实矽中介层不仅可以提供高阶数位应用高效能的表现,实际上也不如印象中的昂贵。(责编:陶圆秀)