NEC向待机零功耗SoC再近一步

来源:华强电子网 作者:—— 时间:2013-02-21 13:59

日本东北大学与NEC于2013年2月19日宣布,已建成“基于自旋电子学技术的逻辑存储器IC”的设计环境。两家单位共同开发出了设计这种IC所需的基本电路库等,完成了与CMOS SoC相同的“RTL→GDS-II自动设计流程”。

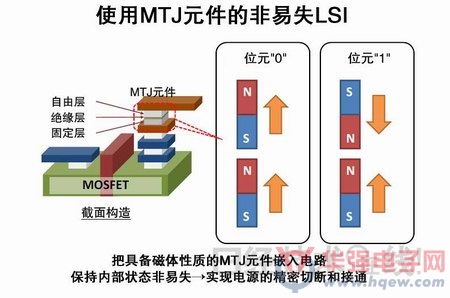

此次的自动设计技术是利用电子具备的负电荷性质以及微磁铁具备的自旋性质的“自旋电子学逻辑IC”技术之一。采用了东北大学长期以来一直在开发的垂直磁化MTJ元件,这种元件对磁性体具有垂直磁化作用,能够保持内部状态的不易失性(图1)。

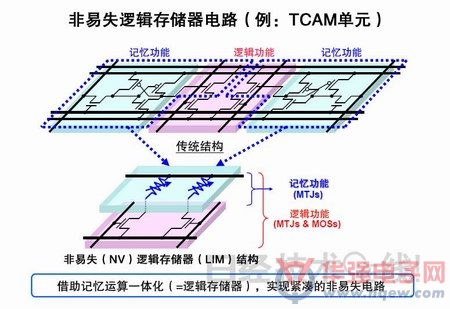

通过采用MJT元件与MOS电路一体化的“NV-LIM(nonvolatile logic-in- memory)”结构,可以实现紧凑的存储器一体型低功耗逻辑IC(图2)。在此之前,东北大学与NEC已经通过设计、试制NV-LIM结构的通用搜索电路(TCAM)、FPGA用LUT(look up table)、加法器等,对MTJ元件和NV-LIM结构进行了评价。但是,由于基本是采用手工设计方式,因此,即使是小规模、重复度高的电路,单是布局设计也需要3~4人1个月的工作量。

图1:MTJ元件。东北大学与NEC的数据。

图2:NV-LIM结构示例。东北大学与NEC数据。

新开发电路库和辅助工具

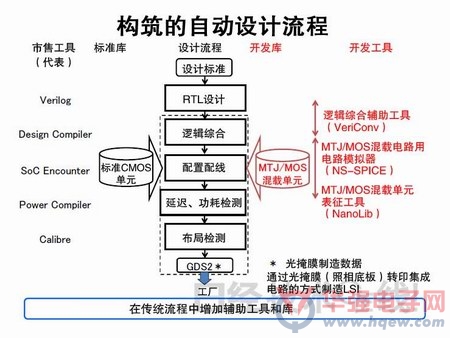

这一次,为了达到“实现待机零功耗SoC”的目标,东北大学与NEC完善了采用MTJ元件和NV-LIM结构的IC的自动设计环境(图3)。通过把(1)新开发的MJT/MOS混载单元的电路库和(2)新开发的辅助EDA工具群与既有的EDA工具群相结合,完成了自动设计流程。

这样一来,就可以采用与现在的CMOS SoC相同的步骤,设计出基于自旋电子学的低功耗SoC。新开发的辅助EDA工具有3种,分别是逻辑合成辅助工具“VeriConv”、MTJ/MOS混载电路用电路模拟器“NS-SPICE”、MTJ/MOS混载单元表征工具“NanoLib”。

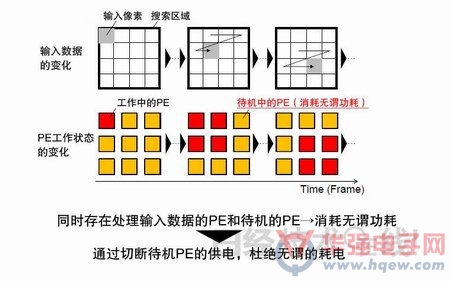

此次,东北大学与NEC利用完善了的自动设计流程,设计了图像处理用处理器阵列IC。该IC是利用串联的处理器(PE,Processor Element),推测多个视频中物体移动量的“运动矢量检测电路”。在阵列中,正在处理输入数据的PE,以及待机的PE同时存在(图4)。切断待机PE的电源就能避免无谓的耗电。因此,该处理器阵列为PE采用了非易失性的NV-LIM结构。这样一来,就可以简单地切断电源,而无需担心数据丢失。

图3:完成的设计流程。东北大学与NEC数据。

图4:处理器阵列的动作。东北大学与NEC数据。

利用90nm的MTJ/MOS混载工艺进行试制

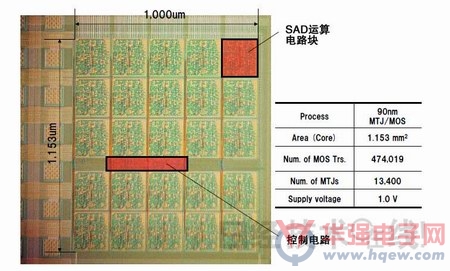

集成了25个PE和控制电路的IC是采用90nm的MTJ/MOS混载工艺试制而成的。在1.153mm2大小的芯片上,要集成47万4019个MOS晶体管和1.34万个MTJ元件。电源电压为1.0V(图5)。

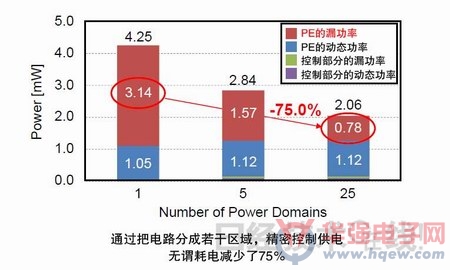

技术人员通过改变试制芯片的电源域数量,确认了NV-LIM结构的效果。结果表明,与电源域数量为1(电源开闭只能以芯片为整体进行控制)时相比,电源域数量为25(PE的电源开闭可单独控制)时,PE的漏电流减少了75%(图6)。

图5:试制的芯片。东北大学与NEC数据。

图6:功耗评价结果。东北大学与NEC数据。

今后,东北大学与NEC还将继续改进自旋电子学逻辑IC技术,研发目标除了开发更大规模、更节能、多用途IC以外,还包括尽早实现该技术的实用化。二者在2013年2月19日(当地时间),在美国加利福尼亚州旧金山举办的“International Solid-State Circuits Conference(ISSCC) 2013”上发表了此次的成果。

- •颠覆性 Cadence Reality 数字孪生平台为人工智能时代的数据中心设计带来变革2024-03-22

- •Vishay推出采用改良设计的INT-A-PAK封装IGBT功率模块,降低导通和开关损耗2024-02-29

- •击败高通!最新全球芯片设计厂商TOP10排名2023-09-25

- •第三届中国集成电路设计创新大会暨IC应用博览会举行2023-07-17

- •【应用引领集成电路产业高质量发展】第三届中国集成电路设计创新大会暨无锡IC应用博览会(ICDIA 2023)7月即将在无锡召开2023-07-05

- •Cadence推出Allegro X AI,旨在加速PCB设计流程,可将周转时间缩短10倍以上2023-04-07

- •最新预判!今年中国集成电路设计业销售同比增长16.5%2022-12-27

- •Qorvo 推出用于 5G 设计的新一代 PA 模块2022-08-16

- •科大讯飞于福建成立新公司,经营范围包括集成电路设计2022-03-24

- •高亮度LED封装散热设计全攻略2011-03-14