超宽带系统中ADC前端匹配电路设计介绍

来源:华强电子网 作者:—— 时间:2013-04-22 10:42

1. 引言

传统的窄带无线接收机,DVGA+抗混叠滤波器+ADC链路的设计中,我们默认ADC为高阻态,在仿真抗混叠滤波器的时候忽略ADC内阻带来的影响。但随着无线技术的日新月异,所需支持的信号带宽越来越宽,相应的信号频率也越来越高,在这样的情况下ADC随频率变化的内阻将无法被忽视。为了取得较好的信号带内平坦度,引入了ADC前端匹配电路的设计,特别是对于non-input buffer的ADC在高负载抗混叠滤波器应用场景下,前端匹配电路的设计在超宽带的应用中就更显得尤为重要。本文将以ADS58H40为例介绍ADC前端匹配电路的设计。

2. Non-input buffer ADC内阻特性及其等效模型

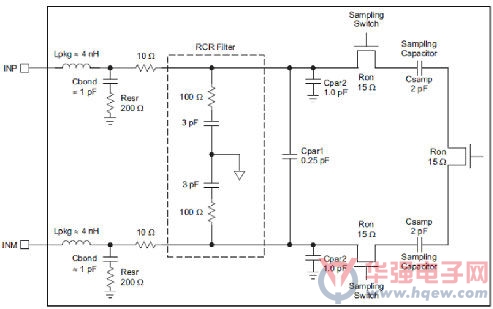

理想ADC的输入内阻应该是高阻态,即在前端抗混叠滤波器的设计中无需考虑ADC内阻带来的影响,但是实际ADC内阻并非无穷大并且会随着频率而发生改变。从输入内阻的角度而言,ADC又可以被分为两类,一个是有输入buffer的ADC,输入特性更趋向于理想ADC,内阻往往比较大;另一类就是没有输入buffer的ADC,它们的内阻在高频不可忽略且随频率发生改变,但它们的功耗比前者要小。图1为non-input buffer ADS58H40模拟输入等效内阻模型。ADC模拟输入端采样保持电路本身所等效的阻抗网络随频率的改变而变化;再加上ADC 采样噪声的吸收电路(glitch absorbing circuit)RCR电路,它的存在改善了ADC的SNR和SFDR,但也使得ADC的内阻随着频率而越发变化。两者效应叠加使ADC的等效负载整体呈现容性。

图1:ADS58H40模拟输入等效内阻模型

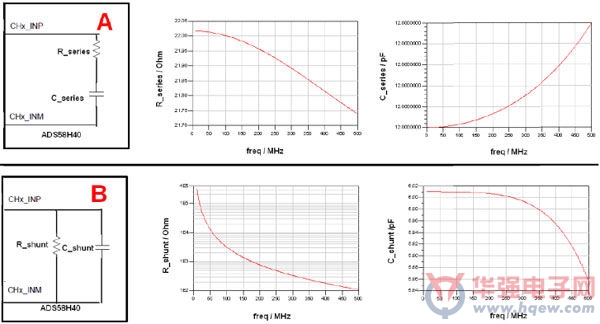

图2以ADS58H40为例给出了内阻随频率变化的曲线图。A串联模型,串联模型中的串联等效电阻值在Ohm量级。B并联模型,并联模型中的并联等效电阻值在低频(<100MHz)的时候kOhm量级,但随着输入频率不断升高(>200MHz),并联等效电阻值会急剧下降到百欧姆级,使其相对于抗混叠滤波器ADC端负载不可忽略。而且不管是并联模型还是串联模型中的等效电容,也使得抗混叠滤波器ADC端负载特性偏离理想的阻性特征需要补偿。

图2:ADS58H40内阻简化模型:A串联模型,B并联模型;及其相关频率变化曲

- •高通推出全新射频滤波器技术,赋能新一代5G和Wi-Fi解决方案2021-10-21

- •Melexis 推出集成红外带通滤波器的 QVGA 分辨率飞行时间传感器芯片2021-09-16

- •TI首款具有集成式有源EMI滤波器的先进直流/直流控制器发布2021-04-07

- •Qorvo推出高性能BAW滤波器,支持Band 41频段5G基站部署2020-09-24

- •国产化滤波器迎重要突破 左蓝微电子TC-SAW改变依赖进口格局2020-09-16

- •Qorvo推出行业首款带BAW滤波器的Wi-Fi 6 iFEM,以实现整个住宅的网络覆盖2020-01-08

- •BAW/FBAR滤波器工艺难度高 国产化向中高端迈进2019-12-30

- •贸泽电子开售面向企业级Wi-Fi 6系统的Qorvo QPF4528前端模块2019-03-26

- •一文预测5G带来的半导体投资机会2019-01-23

- •调整简便且稳定的有源滤波器2019-01-23