超宽带系统中ADC前端匹配电路设计介绍

来源:华强电子网 作者:—— 时间:2013-04-22 10:42

3. Non-input buffer ADC前端匹配网络拓扑架构

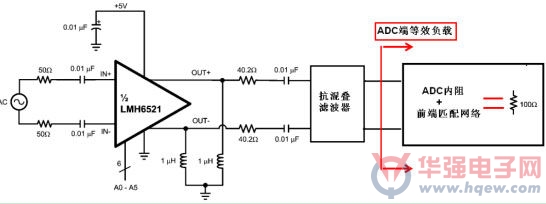

由于ADC的等效内阻随频率变化而且在高频时偏离理想高阻态,抗混叠滤波器ADC端负载阻抗的选择就显得尤为重要。理想ADC支持抗混叠滤波器的负载的任意选择,完全没有要求。但是内阻的变化,使得现实中ADC希望前端的抗混叠滤波器的负载阻抗可以比较小,即传统50Ohm抗混叠滤波器的设计,ADC的kOhm级的内阻相对于50Ohm而言可以忽略不计。但是现在越来越多的抗混叠滤波器需要100Ohm的负载设计,以达到前端驱动级的最优工作状态。图5以现在无线基站设计中常用的DVGA LMH6521为例,为了使整个接收链路达到最优的线性性能,推荐使用100Ohm的抗混叠滤波器。此时如果仍采用简单的100Ohm负载并联在ADC输入端的做法,随着输入信号频率的升高和输入信号带宽的增宽,ADC内阻非理想特性将越来越明显,它会直接拉低ADC侧的100Ohm负载,恶化信号的带内平坦度。

图3:DVGA最优工作状态负载要求示意图

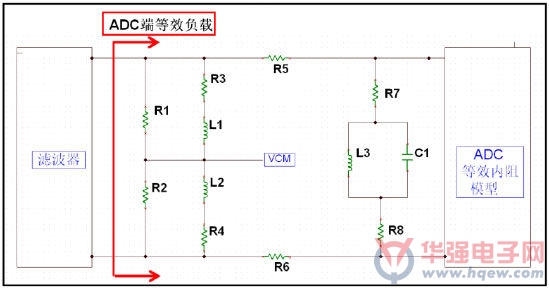

为了统一抗混叠滤波器的设计以简化其在不同平台项目中的移植,希望ADC侧(包括ADC等效内阻和前端匹配电路)在整个信号带宽中都呈现一致的阻抗特性例如图3应用中的100Ohm, 引入了ADC前端匹配网络如图4所示。

图4:Non-input buffer ADC前端匹配网络拓扑架构简图

其中,

1) R1和R2是ADC侧阻抗的主要组成部分,在假设ADC理想高阻特性的情况下,它即代表了ADC侧的负载。由于ADC有限内阻和所需的匹配网络,为了达到整体效果仍保持100Ohm负载状态,R1和R2远高于50Ohm的最优取值。R1和R2不仅决定了ADC输入pin脚的实际共模电压(VCM-Analog input common mode current*R1, ADC的性能SNR和SFDR会随着VCM的变化而发生些许改变);而且原本也是sampling glitch的低阻泄放路径,所以不宜过大。R1和R2的取值原则为实现ADC端组合负载目标前提下的最小值,而且最大值不宜超过100Ohm。

2) R5和R6代表ADC输入口串联的5Ohm或者10Ohm的阻尼电阻,为的是衰减可能由bonding wire寄生电感引起的震荡。

3) 由R3-L1-L2-R4组成的网络主要是负责超宽带应用中的带内平坦度调整,它存在的意义在于此网络呈感性,阻抗随频率递增;它和随频率递减的ADC等效内阻呈反方向变化,两项并联使整体阻抗在所需频率范围内尽量保持不变。如果觉得网络过于复杂,也可以考虑将L1和L2合并为一个电感断开VCM连接;考虑分隔为两个电感仅是为VCM电流提供和R1+R2 并行的通路以减小VCM距理想值的偏移。

4) R7-L3//C1-R8组成的网络则主要担负吸收sampling glitch的责任。在50Ohm负载抗混叠滤波器的应用中,50Ohm负载路径即相当于采样噪声的低阻泄放路径,所以R-L//C-R电路选配一般可以不加,但是当抗混叠滤波器的负载阻抗增加,例如上文中所提到的100Ohm抗混叠滤波器的应用,R-L//C-R的网络在性能要求较高的应用中建议采用。采样噪声是由采样开关的开关切换引起的。只有在ADC输入pin脚处直接引入低阻通路才可以有效的将其吸收,这就是为何RLCR网络需要尽可能的接近ADC输入管脚布局。否则,采样噪声会在dither的作用下转化为影响ADC性能的噪声从而恶化SNR和SFDR。此吸收采样噪声电路的最主要的组成部分为电容,采样噪声多为高频分量组成,对其形成低阻通路即低通电路或带通电路(对有用信号为高阻,对高频噪声为低阻)。C的取值不易过小,过小影响吸收效果,同样也不易过大,过大会严重影响输入带宽。两端串联的R不易过大25Ohm为宜,并联的电感主要是降低Q值,有助于平坦带内波动。当R3-L1-L2-R4和R7-L3//C1-R8网络共存的时候,出于带内平坦度的考量,需要移去L3形成R-CR网络。

- •高通推出全新射频滤波器技术,赋能新一代5G和Wi-Fi解决方案2021-10-21

- •Melexis 推出集成红外带通滤波器的 QVGA 分辨率飞行时间传感器芯片2021-09-16

- •TI首款具有集成式有源EMI滤波器的先进直流/直流控制器发布2021-04-07

- •Qorvo推出高性能BAW滤波器,支持Band 41频段5G基站部署2020-09-24

- •国产化滤波器迎重要突破 左蓝微电子TC-SAW改变依赖进口格局2020-09-16

- •Qorvo推出行业首款带BAW滤波器的Wi-Fi 6 iFEM,以实现整个住宅的网络覆盖2020-01-08

- •BAW/FBAR滤波器工艺难度高 国产化向中高端迈进2019-12-30

- •贸泽电子开售面向企业级Wi-Fi 6系统的Qorvo QPF4528前端模块2019-03-26

- •一文预测5G带来的半导体投资机会2019-01-23

- •调整简便且稳定的有源滤波器2019-01-23