频率合成器的高性能架构实现技术

来源:华强电子网 作者:—— 时间:2013-05-15 10:19

架构的改变在取得快速频率切换时间时也非常有用。PLL稳定到一个新频率所需的时间反比于环路带宽。在简单架构中,对小的信道频率间隔要求意味着使用窄的环路带宽,这将导致环路的频率步长稳定时间变慢。在基于整数PLL的设计中,参考频率将等于这个频率步长,而且环路带宽必须比这个步长小大约一个数量级。在基于小数N的设计中,虽然参考频率可以保持高得多的值,但环路滤波器通常仍然必须对落在步长倍数处的信号进行高衰减,从而对环路带宽设置了一个上限。然而,通过将DDS用作PLL内的高频参考源,分频比可以保持低值(这样可以最大限度地减小噪声),同时无需约束环路带宽就能实现非常小的频率步长。

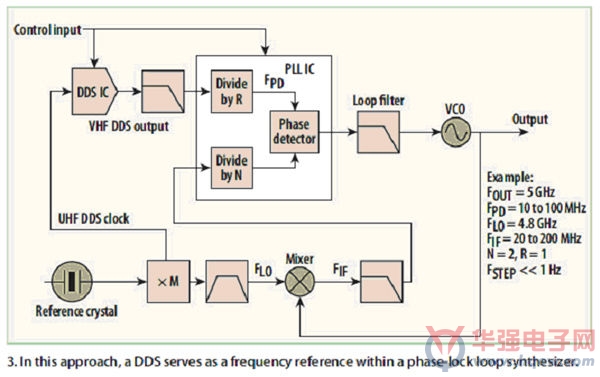

现代DDS IC可以用很小的外形封装产生甚高频(VHF)范围内的输出,并且具有MHz级的调谐步长和优秀的相位噪声。频率和相位调制功能通常也包含在内。近端杂散信号电平取决于相位查找表分辨率和输出数模转换器(DAC),而且一般都非常好(约-80dBc);然而,在输出端会呈现电平很高的其它取样信号。通过将DDS IC用作PLL中的频率参考源,输出频率可以转换成需要的任何频率,多余的取样信号也可以被PLL高效地滤除。图3显示了这种架构的例子。

图3:在这种方法中,DDS用作锁相环合成器中的频率参考源。

PLL可以认为是提供跟踪滤波功能,这是很有益的,因为它能极大地衰减DDS输出端的多余取样信号以及由下变频过程产生的其它信号。根据可以容忍的杂散信号电平,可以要求PLL对电平已经很低的近端杂散信号进行少许衰减或不做额外衰减。这样,PLL的环路带宽可以保持比传统PLL合成器中的实际带宽大许多,从而提高频率切换速度。PLL参考频率可以做得比DDS频率步长高出许多,分频比则非常小,从而实现优异的相位噪声性能。由于更大的环路带宽等同于特定偏移处更大的环路增益,而且来自相位检测器的噪声贡献更低,因此VCO贡献的噪声成份也可以得到有效降低。

下一篇:无线充电 助您摆脱麻烦充电器

- •【会议议程】12月19-21日2022(十四届)传感器与MEMS产业化技术国际研讨会(暨成果展)佛山南海瞻云酒店召开2022-12-16

- •FORESEE XP1000 PCIe SSD开启Gen3后时代发展之路2021-08-02

- •FORESEE工规级SSD应用宽温技术,加速智能工业场景落地2021-07-21

- •基于J750EX测试系统的SRAM VDSR32M32测试技术研究2017-09-05

- •Vishay检查表: 采用安规电容防止过载的12点注意事项2017-07-28

- •汽车系统的USB供电2017-06-08

- •适用于 FPGA、GPU 和 ASIC 系统的电源管理2017-05-11

- •一文读懂SPI串行外设接口2017-04-27

- •TLV3501滞回比较器电路设计2017-04-14

- •ZigBee无线呼叫系统硬件电路2017-04-05