实时签核反馈在AMS设计中的价值

来源:电子工程专辑 作者:—— 时间:2014-02-17 11:20

过去10年,先进IC节点的设计规则手册从几十页的小册子扩充为几百页的一本书。这种扩充源自于图层数量的大幅增多(有11层或更多金属层的情形也不稀奇)、各层检查项目的增多、以及这些检查复杂性的大幅增大。这对模拟和定制化IC设计工程师有着巨大影响,一方面他们要努力优化设计达到最佳性能,同时必须确保设计版图符合规则。

客户挑战:缩小验证差距

定制化设计的流程一直是以反复的方式进行的——绘制一部分版图、检查版图的DRC、LVS及功能验证、修正错误、然后重复这个过程,直到所有DRC错误都得到修正(图1)。当DRC检查很简单时,这一步很安全,并且不怎么妨碍从构建版图到原理图的过程。

图1.传统的设计-检查-修正循环。

然而,随着设计规则数量和复杂性的增加,定制化设计工程师不再能够有效率的记住所有的设计规则。这样,每次循环的动作都可能带来新的DRC错误。花在“修正”原始版图上的时间就增加了,这样,版图工程师就没有更多时间用于绘制最佳版图,从而获得最佳的性能和面积。事实上,从事32nm及以上节点设计的设计团队都发现,要得到一个完全没有DRC错误的高品质版图,困难程度是越来越高。

定制化设计工具包含多种内建DRC工具,辅助版图工程师放上多边形。在这些“工具内”DRC检查程序里最著名的是Cadence的pA工具,但所有的定制化工具都具备相似的功能,比如SpringSoft的Laker工具有“基于规则的设计”,Synopsys的Custom Designer有Smart DRD。

尽管所有这些工具都有着类似的功能,但没有一款能涵盖全部签核DRC检查,也没有一款得到晶圆代工厂的签核资格认可。随着签核文件(deck)与LEF、内建DRC检查工具的能力之间的差距越来越大,版图工程师得到干净的设计需要耗费的时间越来越多,而花在新版图上的时间越来越少。定制化设计团队被迫在下面三种鸡肋方案中进行选择:

1. 他们可以对设计进行少一点优化——达到“DRC干净”的版本就打住。因为“版图品质”难以衡量,采用这种方法“失去机会”成本尽管现实,却不太好定量确定,但在未来某个时间会出现潜在的性能问题。设计者知道将来一定会有后果,但不知会在何时何处出现。

2. 他们可以花更长时间来完成版图。然而,随着里程碑日程表的流逝,对设计团队和公司的潜在影响会变得明显。对于珍爱自己工作的工程师来说,这条路很危险。

3. 他们可以雇佣更多工程师。虽然这种方法可以让公司一切如常地维持,即使采用低成本的资源,但它却是一种代价高昂、而结果并不确定的选择。更多工程师不是总能确保更快或更好的设计。

在编辑定制化设计时执行签核检查

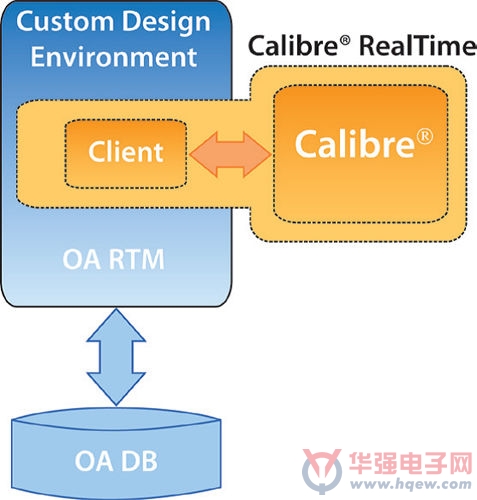

为了对这种情形做出补救,设计者需要采用一种交互式工具,能在创建版图时对照整个签核DRC文件(deck)检查他们的版图设计。作为这种方法的一个示例,我们来看Calibre RealTime工具在设计师的环境中是如何工作的(图2)。它使用OpenAccess运行时模型(OA RTM)来接收来自定制化设计工具的变化事件通知,然后检索相应的几何图形来进行DRC检查。然后它自动运行单层模式的Calibre nmDRC。DRC引擎针对正在编辑的形状以及附近图形执行快速、增量检查,对设计规则违反情况以及由推荐规则来衡量的潜在系统变化敏感性做出几乎瞬时的反馈。检查的结果可以直接在设计工具的用户界面上高亮显示。

通过这种方法在版图创建的过程中将签核结果即时提供给版图工程师,消除了设计-检查-修正循环的时间损失,得到高品质的版图。因为它采用同样的标准晶圆代工厂认可DRC文件(deck),因此在实时结果与签核DRC间的关联方面毫无疑问。

图2。Calibre RealTime集成的体系结构。

Calibre RealTime工具在设计环境中提供一个新的工具栏,让版图工程师在他们的设计工具中工作并专注于创建高品质版图,而签核DRC检查在创建高品质版图中成为一个几乎隐形的后台实时运行程序。

这种方法能使用签核DRC引擎来执行所有的检查,包括推荐规则检查、模式匹配规则检查、基于方程的DRC和双重成像(double patterning)规则检查,让定制化IC设计师们能在版图生成过程中纠正和调整其设计,以产生没有DRC错误、能抵御制造工艺变动问题、并经过优化达到最令人满意的性能和工作特性的设计。

下一篇:超级电容在混合动力汽车中的使用

- •华为做ARM服务器芯片能否撼动Intel X86服务器的地位?2016-01-27

- •台湾半导体应适当向大陆开放:不然将被全面封杀2016-01-15

- •拓墣:晶圆代工产值 明年增2%2015-12-22

- •台IC设计产业今年产值估减9.5%、明年减1.4%2015-12-11

- •大陆今年恐挤下台湾成IC设计全球第二2015-12-10

- •IC设计业销售额翻倍增长,9家企业跻身全球50强2015-12-03

- •分析师预估2015年全球IC设计业产值增3.8%2015-07-28

- •大陆将“挖”塌台湾半导体产业?2015-07-07

- •台IC设计全年获利恐倒退 晶圆代工产能松弛2015-07-07

- •台系IC设计厂商见缝插针 渗入大陆红色供应链2015-06-24