如何采用门控时钟来设计低功耗时序电路

来源:华强电子网 作者:------ 时间:2014-07-03 14:13

电路运算

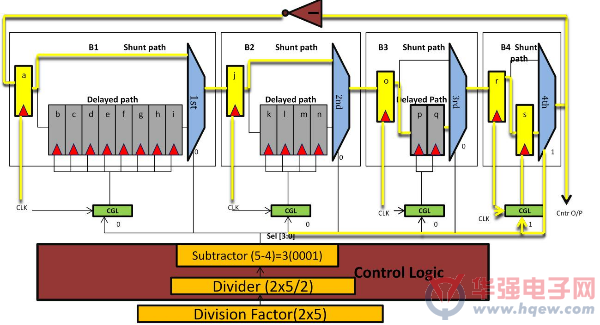

以分频因子为10(即2N=10)的电路为例。由于传统约翰逊计数器在分频因子为2N时需要N个触发器,要使分频因子为10,电路中需要2N/2 = 10/2 = 5个触发器。分频器电路的输出是2N/2 = 5,这时减法器的输出则为(5-4) = 1,再馈入多路复用器的选择线路,其二进制表示为0001。这个4位sel[3:0]=0001信号极为重要,因为它不仅控制着门控时钟逻辑,还在分流和延迟路径中做出选择。

图4:分频因子为10的电路运算

在这种情况下,只有Sel[0]会变为1并启用s触发器的时钟,并且同样地,sel[3]、sel[2]、sel[1]将相应禁用 (b、c、d、e、f、g、h、i)、(k, l, m, n)、(p、q)触发器的时钟,见图4中突显部分。另外需要注意的是,“a, j, o 和r”触发器将始终启用。这样一来,不仅启用了所需的触发器,并且该电路可在第4个多路复用器的输出上获得所需的输出时钟。因此,在这个示例中,共有5个触发器接收到时钟,其他触发器的时钟将自动被禁用。

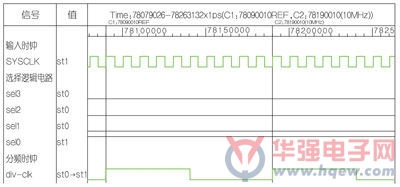

我们对上述计数器进行了模拟,其结果以RTL波形的形式呈现在图5中。根据图5可以推出:修改后的计数器采用sel[3:0]作为4’h0001,将一个100 MHz的时钟进行分频,提供10 MHz的输出。

图5:分频因子为10的波形

- •【会议议程】12月19-21日2022(十四届)传感器与MEMS产业化技术国际研讨会(暨成果展)佛山南海瞻云酒店召开2022-12-16

- •FORESEE XP1000 PCIe SSD开启Gen3后时代发展之路2021-08-02

- •FORESEE工规级SSD应用宽温技术,加速智能工业场景落地2021-07-21

- •基于J750EX测试系统的SRAM VDSR32M32测试技术研究2017-09-05

- •Vishay检查表: 采用安规电容防止过载的12点注意事项2017-07-28

- •汽车系统的USB供电2017-06-08

- •适用于 FPGA、GPU 和 ASIC 系统的电源管理2017-05-11

- •一文读懂SPI串行外设接口2017-04-27

- •TLV3501滞回比较器电路设计2017-04-14

- •ZigBee无线呼叫系统硬件电路2017-04-05