目前半导体产业面临的挑战究竟有哪些?

来源:华强电子网 作者:—— 时间:2012-06-20 08:59

在28奈米节点,包括随机掺杂扰动(randomdopantfluctuations)、线宽、线间距变动,以及导孔电阻值(viaresistance)等会影响RC相关时序的种种问题,为目标规格带来不可预知且低落的参数良率。这种制程变异带来不断增加的漏电、功耗与良率等冲击。

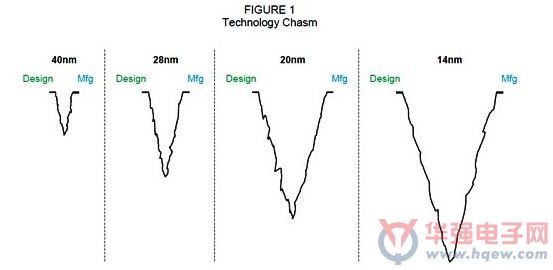

为了弭平图中所示的鸿沟,晶圆代工厂的制程技术团队与无晶圆厂晶片供应商设计团队之间,需要有一个IDM形式的沟通介面。大型无晶圆厂晶片业者与晶圆代工厂,具备建立该种介面的财源,也能合作解决问题;但是较小型的厂商将会面临财务挑战。不过关键是,谁应该负责建立那种IDM形式的沟通规则,并支付所需成本?是无晶圆厂业者、晶圆代工厂,还是两边都要负担?看来其中有很多都是需要双方共享的。

半导体制程演进过程中,晶圆代??工厂与无晶圆厂业者之间的技术鸿沟越来越深

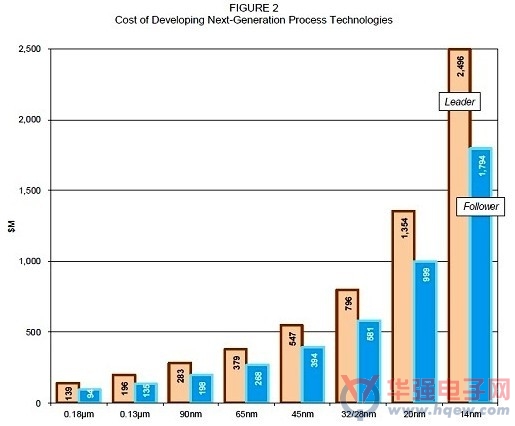

要成为晶圆代工产业龙头,所需支出的资本越来越高:

台积电(TSMC)的2012年资本支出为80亿美元,也就是每1万片晶圆需要10亿美元成本,以因应每月8万片晶圆的28奈米与20奈米制程额外产能。三星(Samsung)的非记忆体业务2012年资本支出金额也在80亿美元左右(官方公布为65亿美元),大约也是供应每月8万片的额外产能。

Globalfoundries则是正在提升Malta晶圆厂的产出,计划在目前Dresden晶圆厂每月8万片晶圆产能之外,再增加每月3万片晶圆的额外产能。至于联电(UMC),其2012年资本支出金额为20亿美元,并宣布其Fab12厂将筹资80亿美元。只有很少数的半导体厂商有能力在14奈米节点投资更大产能所需的成本,因此无晶圆厂晶片供应商也会去选择最佳的合作对象。

随着晶片微缩,制程技术复??杂度也更高:

无论是对IDM厂商或是晶圆代工业者来说一个很大的问题是,随着晶片微缩,开发先进制程技术的成本也越来越高,如下方图所示。在20奈米节点,主要的成本来自于bulkCMOS技术,但到了14奈米节点则是FinFET(已知英特尔在22奈米节点就使用FinFET)。

下一篇:“价格战”正在搅动整个芯片产业链

- •不撤反进?欧洲大厂深度绑定中国供应链,释放重要信号2026-03-24

- •2026半导体大爆发:全球销售预计首破1万亿美元!AI赋能新时代2026-02-10

- •涨价潮背后,全球半导体迎“超级周期”2026-01-29

- •2500亿美元!美国和中国台湾芯片贸易协定落地,全球半导体格局正在改写2026-01-19

- •重磅消息 | 美国宣布对部分进口半导体及制造设备加征25%关税2026-01-16

- •2025年电子元器件行情分析与2026年趋势展望2026-01-08

- •美国按下“暂停键”:对华半导体征税推迟18个月2025-12-24

- •2026年全球半导体市场逼近1万亿美元大关2025-12-10

- •全球半导体产业再现强劲增长!2025-11-04

- •全链聚合,智创未来!深圳华强全“芯”阵容,实力亮相ES SHOW!2025-10-30