五大技术降低未来IC功耗

来源:华强电子网 作者:—— 时间:2013-04-01 10:10

采用3D/光学互连

透过缩短互连线的长度并降低其电线,就能支援更小的驱动器电晶体,从而降低IC的功耗。缩短互连线长度的传统方法是增加金属层,因此目前有些芯片的金属层多达10层。

然而,互连层设计最新创新成果是三维硅穿孔(TSV),允许将记忆体芯片堆叠在处理器之上。这种技术将互连长度减少到芯片间的距离,因此不需要大功耗的驱动电晶体和长的印刷电路板互连线。然而,TSV的经济性比较差,目前大多数芯片制造商的TSV时程都处于延后状态。

“虽然硅穿孔(TSV)确实可透过缩短走线长度来降低功耗,但这是一种成本非常高的解决方案。”TI公司的Greenhill表示,“为了更具经济性,TSV需要能够弥补其它不足(如介面性能),才能让它的成本较为合理。”

赛灵思公司(Xilinxnc.)是一家非常瞭解如何为TSV成本/性能取得平衡的公司,该公司正提供第一款使用TSV的商用芯片。相较于在PCB板上焊接独立元件的方式,赛灵思公司采用这种具成本效益的方案不仅能降低芯片功耗,同时也提升了性能。此外,它还可为赛灵思公司的客户降低BOM成本,赛灵思公司资深总监EphremWu表示。

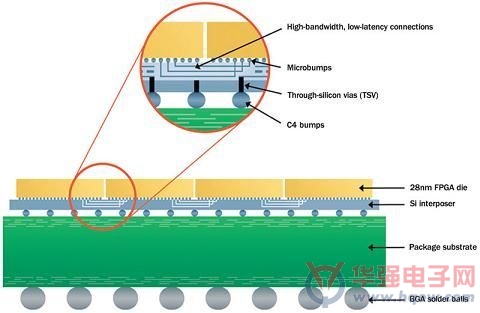

图4:赛灵思公司能够使用台积电的硅插入器在封装内互连4个FPGA,从而使功耗从112W降低到19W。来源:赛灵思

赛灵思公司透过使用硅中介层(interposer)迴避了在PCB板上焊接各个FPGA的问题。这种硅中介层可在单一封装内互连4个高密度的FPGA。

这种技术不仅能提升性能,还能使功耗降低到19W,相形之下,传统的PCB解决方案功耗还高达112W。另外一种前端技术是使用光学收发器。例如,IBM公司的Power7超级电脑使用从传统光学元件产生的板载光子互连。未来的芯片很可能使用Kotura公司和其它公司提供的专用光学解决方案,将光子功能转移到能够附加处理器与记忆体芯片的微型光学芯片上。

“我们的低功耗硅锗元件整合了透镜、滤波器、调变器以及你需要的所有其它光学元件于单颗芯片上。”Kotura公司行销副总裁ArlonMartin指出。

Kotura公司的硅光子制程使其得以将大约香烟盒大小约1万美元的传统光学收发器单元整合进最新款iPhone大小的500美元封装中,使用的功耗更低4至20倍。Kotura公司还展示该公司的SiGe收发器可透过堆叠式CMOS芯片间的气隙传送光学讯号,最终在堆叠芯片之间形成一个高速、低功耗的光学资料通道,适用于代替PCB走线。

上一篇:如何在FPGA中实现状态机

下一篇:射频设计中的热量管理

- •英特尔重大人事变动!董事长即将离任,芯片巨头进入关键转型期2026-03-10

- •英特尔:内存芯片短缺或将持续至2028年!2026-02-06

- •英特尔安装全球首台商用High-NA EUV光刻机!14A进程冲刺量产,制程革命近在眼前2025-12-23

- •突发!英特尔、AMD、德州仪器遭乌克兰平民诉讼!芯片“流向战场”引爆法律风暴2025-12-17

- •英特尔股价暴涨 — “昔日王者”能否东山再起?2025-12-04

- •瑞萨携手英特尔,为英特尔全新酷睿Ultra 200V系列处理器 打造先进电源管理解决方案2024-10-24

- •英特尔一季度财测低于预期 2023年Q4 PC业务增长33%2024-01-26

- •突发!英特尔推中国版芯片替代英伟达!2023-11-08

- •缺钱的千亿芯片巨头——英特尔的灾难2023-10-25

- •艾迈斯欧司朗新一代彩色激光器问世:在持续提升光束质量的同时减小电源功耗2023-07-11