五大技术降低未来IC功耗

来源:华强电子网 作者:—— 时间:2013-04-01 10:10

降低工作电压

微缩芯片尺寸通常能够降低工作电压,从而实现节能。例如,三星公司(Samsung)最新的20nm‘绿色记忆体’芯片透过将工作电压从1.5V降低至1.35V,以节省67%的功耗。

处理器和逻辑电路的工作电压甚至低于记忆体元年,但工作电压降低至1V以下时就不可避免地必须进一步改善半导体制程。IBM、英特尔(Intel)、三星、TI、台积电(TSMC)和其他每家半导体制造商均持续改善制程,以便能在更低电压下作业,不过,过去几个制程世代以来的进展速度已开始减缓。

其关键在于电晶体导通的阈值电压在使用不同晶圆时是不一致的,因为在更大尺寸时制程的变化可以忽略。而由于在特定电压下关断状态的漏电流在不同阈值时有很大的变化,因此理想芯片实际上要使用根据其特性定制的供电电压。

英特尔公司声称已具有更好的解决方案──这是该公司花费近十年时间进行完善的一种方案。英特尔采用了所谓三闸(tri-gate)的3DFinFET电晶体架构,这种架构以三维方式在电晶体通道周围环绕三个金属闸极,使电晶体处于这些闸极的电场之下。这种技术可以抵销阻止工作电压低于1V的制程变化。

“我们已经成功地展示我们的三闸电晶体结构,可将工作电压减少到0.7V範围,而且还能做得更低。”英特尔公司资深工程师MarkBohr指出,“这些都是具有更陡峭次阈值斜率的完全耗尽型电晶体,可以更小的漏电流更快切断,同时以更低阈值导通电压。”

资金雄厚的半导体制造商们专注于模拟英特尔公司的3D架构,但一些新创企业则致力于研发新型平面制程,针对缺乏时间和资金来完善3D架构的半导体制造商重启电压调整进程。例如SuVolta公司已经发明出一种用于标准CMOS产品线的超低电压平面制程。

SuVolta并未使用3D闸极耗尽型电晶体,改而采用一种未掺杂通道(带掺杂的阈值和保护带)以避免掺杂中的变化。深度耗尽型通道制程可在标准的平面CMOS产品线上实现。

“透过使用平面深度耗尽型通道制程,我们已成功展示供电电压可降低到0.6V,未来还能够降得更低。”SuVolta公司技术长ScottThompson透露。

SuVolta还取得了第一个授权协议──富士通半导体,该公司将在今年稍晚进行量产。

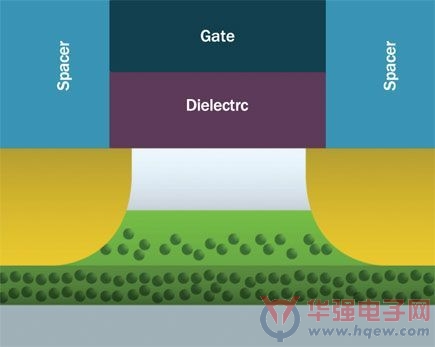

图2:透过采用未掺杂电晶体通道(位于中间的白色区域,在浅绿色的轻掺杂阈值区以及深绿色的重掺杂筛选区上方),SuVolta公司的平面CMOS制程可望使半导体电压进一步降低。来源:SuVolta公司

上一篇:如何在FPGA中实现状态机

下一篇:射频设计中的热量管理

- •英特尔重大人事变动!董事长即将离任,芯片巨头进入关键转型期2026-03-10

- •英特尔:内存芯片短缺或将持续至2028年!2026-02-06

- •英特尔安装全球首台商用High-NA EUV光刻机!14A进程冲刺量产,制程革命近在眼前2025-12-23

- •突发!英特尔、AMD、德州仪器遭乌克兰平民诉讼!芯片“流向战场”引爆法律风暴2025-12-17

- •英特尔股价暴涨 — “昔日王者”能否东山再起?2025-12-04

- •瑞萨携手英特尔,为英特尔全新酷睿Ultra 200V系列处理器 打造先进电源管理解决方案2024-10-24

- •英特尔一季度财测低于预期 2023年Q4 PC业务增长33%2024-01-26

- •突发!英特尔推中国版芯片替代英伟达!2023-11-08

- •缺钱的千亿芯片巨头——英特尔的灾难2023-10-25

- •艾迈斯欧司朗新一代彩色激光器问世:在持续提升光束质量的同时减小电源功耗2023-07-11