DRAM领域遭遇制程极限 求突破

来源:EEtime 作者:—— 时间:2013-06-13 09:32

根据拆解分析机构 Techinsights 最近对目前市面上先进DRAM记忆体单元(cell)技术所做的详细比较分析发现,虽然已有部分预测指出 DRAM 记忆体单元将在 30奈米制程遭遇微缩极限,但各大DRAM制造商仍将持续朝2x奈米甚至1x奈米节点前进。

Techinsights 最近分析了包括三星(Samsung)、SK海力士(Hynix)、美光(Micron)/南亚(Nanya)与尔必达(Elpida)已量产的3x奈米SDRAM记忆体单元阵列结构之制程技术与元件架构,推论该技术仍有进一步微缩的空间,而共同解决方案是结合埋入式字元线(buried wordlines,b-WL)与鳍状存取电晶体(fin-shaped access transistors)。

Techinsights指出,在DRAM单元架构发展时程表上,目前的低3x奈米节点在制程技术整合上的最重要元素,是如何有效提升存取MOSFET的通道长度(channel length),以及如何将DRAM单元阵列上的储存电容区域(storage capacitor area)微缩。

而拥有鞍型(saddle shaped)──或大型鳍式(bulky fin-type)──通道配置的埋入式金属字元线,是推动3x/2x奈米存取电晶体继续微缩的关键解决方案,因为具备控制良好的阈值电压(threshold voltage)以及超低泄漏电流;此外,该种架构的元件具备较大通道宽度与长度,对短通道效应与较高的启动电流(on-current)有较佳的免疫力。

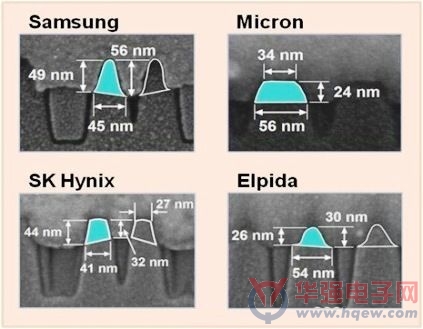

上述四家记忆体厂商都是采用类似的制程生产内凹(recess)、鳍式电晶体;该种鳍状电晶体如下图所示。美光与SK海力士的大型鳍式电晶体外观有点类似梯形,而根据整合通道宽度与长度的估计,美光/南亚的单元电晶体通道宽度最大,尔必达电晶体的通道长度是最长的。

比较三星、SK海力士、美光/南亚与尔必达四家厂商的记忆体单元电晶体架构

在埋入式字元线闸极材料部分,三星是采用电阻高于钨(tungsten,化学符号为W)的TiN金属,与其他三家厂商不同;在字元线堆叠部分,所有厂商的记忆体元件都是采用以钨为基础的材料,不过钨层与多晶矽层之间的屏障材料,则各家厂商都不相同。

储存电容微缩

为了微缩储存电容,金属-绝缘-金属(metal-insulator-metal ,MIM)电容器需要相对应于约当次1奈米厚度二氧化矽(SiO2)的特定电容量,以及高K电介质(high-k dielectrics)、超低泄漏电流,以及高度保角(highly conformal)沉积方法。

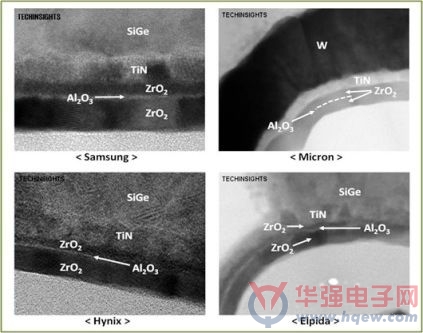

在二氧化锆(ZrO2)层之间加入一层超薄的三氧化二铝(Al2O3),以及W/TiN电极,是制作3x奈米记忆体单元的关键解决方案。Techinsights指出,所有记忆体大厂都藉由采用相同的TiN (阳极)-ZrO2-Al2O3-ZrO2-TiN (底层电极)多层堆叠电容──称为ZAZ-TIT电容,来克服3x奈米记忆体单元的制造挑战(如下图)。

各家厂商的记忆体单元电容结构

在二氧化锆层之间加入薄薄的三氧化二铝,是为了抑制泄漏电流;该电介质在3D圆柱状电容器节点的物理厚度,则是制程进一步微缩的另一个挑战。大多数3x奈米DRAM单元电容器,是采用整体厚度约7~9奈米的多层式电介质,这意味着未来1x奈米DRAM单元架构将会迫切需要进一步缩减该物理性电介质厚度。

多数厂商在TiN顶部电容器上采用矽锗(SiGe)层,除了美光/南亚是采用钨层。SK海力士采用了双层式的多晶矽插栓(plug),来连结储存节点与汲极区(drain region),尔必达则是采用双层W/TiN与多晶矽插栓。

采用机械强化储存高度(Mechanically Enhanced Storage Height,MESH)结构可增加记忆体单元的高度,以支撑电容器;三星、SK海力士与尔必达在这部分都是采用单层氮化物,美光/南亚则是采用双层氮化物来支撑圆柱状电容。根据估算,SK海力士的SDRAM20单元比其他厂商元件拥有更大的记忆体单元电容量。

在阵列区采用三阱制程

Techinsights的拆解分析也发现,大多数埋入式字元线SDRAM元件,在阵列区(array region)都是采用三阱制程(triple well process);这种技术是在p型基板上,将一个p型阱(p-well)嵌入到n型阱(n-well)中。

不过美光/南亚的31奈米SDRAM单元阵列,则是采用「四阱(quadruple well)」制程,也就是在一个较深的p型阱上,将一个较浅的p型阱嵌入较深的n型阱,该较深的p型阱则是位于轻微掺杂(lightly doped)的块状n型基板内。

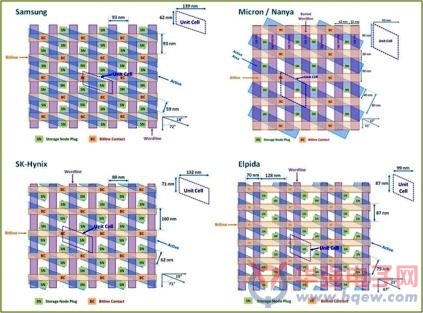

由该种6F2记忆体阵列单元的布局图来看,不同厂商元件的活性(active)/浅沟渠隔离(Shallow trench isolation,STI)形状、倾斜角度(slanted angle)与字元线沉积各自不同,如下图所示。

各家厂商6F2记忆体单元阵列布局图比较

三星与SK海力士拥有相同的交错虚线(staggered dash-line)形式活性区布局设计,与美光/南亚的直线式活性区布局不同,但前者需要额外的隔离字元线。美光/南亚元件的活性区图案倾斜角度比其他厂商都大,这意味着记忆体单元的储存节点触点(storage node contact)与STI间距(pitch)有更大的空间可以利用。

为因应来自智慧型手机、平板装置等非PC装置对DRAM的强劲需求,以及PC用DRAM市场的稳定成长,DRAM记忆体单元架构的进一步微缩确实有其必要。

拜新一代半导体制程与元件设计技术之赐──包括高数值孔径氟化氩(high-NA ArF)浸润式微影技术与双重图形(double patterning)、大型鞍鳍式电晶体(bulky saddle-fin transistors)与埋入式字元线等──DRAM单元阵列可望持续朝30奈米甚至20奈米节点以下微缩。

有一种无电容(capacitor-less) DRAM单元架构,包括将浮体单电晶体DRAM (1T-DRAM)结合绝缘上覆矽(SOI)技术,正在针对20奈米以下制程节点进行开发;同时,所谓的1T-1C (单电晶体-单电容) DRAM记忆体单元制程整合技术也已经足够成熟,可运用于20奈米甚至20奈米以下节点,只要产业界能开发出、并进一步最佳化电容电介质。

拥有较大的通道长度与宽度之无捕陷(Trap-free)超高介电值(ultra high-k)材料与更深的埋入式字元线架构也有其必要;为了迈向1x奈米DRAM记忆体单元阵列,产业界将会需要锁定替代性的单元设计架构,例如4F2、垂直单元架构,以及用薄体SOI无电容单元(thin-body SOI capacitor-less cel)取代目前具备圆柱形电容的埋入式字元线鞍鳍式FET。

上一篇:4G:国产手机厂商重塑品牌的机会

- •主板制造商再次下调出货目标2022-06-07

- •传联电22nm高压制程最快明年首季试产验证2021-12-13

- •应用材料将协助全球领先的SiC芯片制造商增加产量2021-09-10

- •贸泽电子2021年上半年新增62家制造商合作伙伴2021-08-06

- •芯片短缺让检测X光机制造商销量翻倍2021-07-16

- •消息称两巨头已抢先当客户,使用台积电3nm制程来测试自家芯片2021-07-05

- •北美半导体设备制造商出货金额持续攀高2021-06-23

- •贸泽电子2020年新增70多家制造商合作伙伴2021-01-13

- •光通信器件制造商芯耘光电完成近4亿元B轮融资2020-09-30

- •贸泽电子于2020上半年新增45家制造商合作伙伴2020-09-15