基于FPGA及NiosII软核处理器的TFT-LCD接口设计

来源:互联网 作者:------- 时间:2014-12-17 14:11

1 引言

随着电子技术的飞速发展,TFT-LCD作为在亮度、对比度、功耗、寿命、体积和重量等综合性能上全面赶上和超过 CRT的显示器件,被广泛用于各种仪器仪表、电子设备及控制领域中。与之相关的显示控制技术也呈现出越来越多的方式。本文以 640*480的数字输入的 TFT_LCD显示屏为例,介绍了一种基于 NiosII软核处理器实现对 TFT-LCD接口的方法。解决了通常情况下必须使用LCD 控制专用芯片才能解决 LCD显示的问题。

2 系统组成

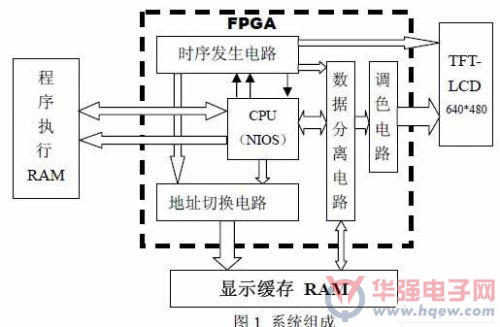

系统框如图 1所示。系统是由 FPGA、显示缓存 RAM、程序执行 RAM及 TFT-LCD组成。 FPGA(用虚线围成)选用的是 ALTER的 EP1C6,RAM采用的是 IDT的 IDT71V547,LCD为 640*480的彩色 TFT-LCD屏。在 FPGA内部是由时序发生、 地址切换、数据分离、调色电路及嵌入式 CPU(NIOS内核)五部分组成。

3各器件的功能

3.1显示缓存 RAM

采用 IDT公司的 IDT71V547 128K X 36bit的 SRAM芯片,工作电压为 3.3V [1]。该芯片作为显示缓存,TFT_LCD读取显示缓存 RAM中的数据并将其在 TFT_LCD上显示。嵌入式 CPU(NIOSⅡ)对显示缓存 RAM的改写就相当于对 TFT_LCD显示内容的改写。

3.2 FPGA

本文 FPGA选用的是 ALTERA公司的 Cyclone 系列中 EP1C6Q240。

3.2.1 时序发生电路

首先由外部输入一相当的频率时钟,通过 FPGA内部的锁相环电路(PLL)生成 100MHz的时钟信号。系统对 100MHz时钟计数生成 50MHz的时钟给嵌入式 CPU(NIOSⅡ)作为嵌入式 CPU的工作主频,同时生成 TFT_LCD所须的场同步时钟、行同步时钟、显示使能时钟和 25MHz的 TFT_LCD主时钟;生成地址切换控制信号、数据分离控制信号,由嵌入式 CPU输出的读写信号产生显示缓存 RAM的读写信号。

3.2.2调色电路

由于文中是以 256色的电路为例,所以,调色电路是将 8位数据译码成 3*6位的三基色数据,调色电路也可以是 ROM型或 RAM型。如果作成 RAM型,可以依据嵌入式 CPU需要显示的图象相应修改调色电路,可显示更丰富的色彩。

3.2.3地址切换、数据分离

此部分电路的作用是:在嵌入式 CPU操作显示缓存 RAM时将地址、数据线切换到嵌入式 CPU,在 TFT-LCD读显示缓存 RAM时将地址、数据线切换到 TFT_LCD。

3.3 TFT-LCD

SHARP公司生产的 *英寸液晶显示屏LQ064V3DG01是较为常用的 TFT-LCD液晶显示屏,它的分辨率为 640×480×RGB[2],具有功耗低、体积小、重量轻、超薄等特点,同时该显示屏是一片真彩显示屏,并属于透光型的 TFT、其亮度高、视角宽、背光灯的寿命也很长,并且采用的是 AG涂层和 260K的彩色显示。可广泛应用于各种仪器仪表及各种视频显示的场合。

4主要电路的设计

4.1时序发生电路的设计

时序发生电路是设计的主要部分。首先,是对系统输入时钟进行频率变换, FPGA(EP1C6)的内部有两个 PLL电路模块,本文用其中的一个来生成 100MHz的时钟。再设计一个 12位的计数器(行计数器),计数 3200脉冲,产生 TFT_LCD的行同步时钟,通过此计数器的计数还可生成 TFT_LCD的显示使能信号(DE)。此计数器的输出还是 TFT_LCD读显示缓存 RAM地址的低 8位(RAM以 32位数据宽度计算)。另设计一个 9位的计数器(场计数器),用其对行同步信号计数又可生成 TFT_LCD场同步的相关信号,同时此计数器的输出可作为 TFT_LCD读 RAM地址的高 9位。

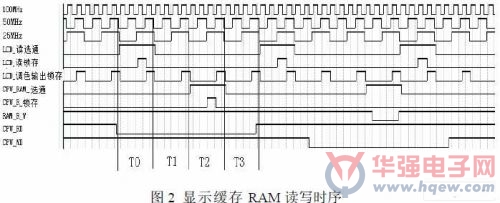

由于嵌入式 CPU与 TFT_LCD是复用一片显示缓存 RAM,所以要对显示缓存 RAM在时间上进行分时控制。由于 IDT71V547是 32位数据宽度的 RAM,如果将 TFT_LCD设计成256色显示,则读显示缓存 RAM一次可显示 4个像素点。所以把行计数器输出的 25MHz时钟作为基准(TFT_LCD主时钟)、以 25MHz的 4个周期(T0、T1、T2、T3,T0=T1=T2=T3=40纳秒)为基本循环,在 25MHz的第一个周期( T0)由 LCD占用产生“ LCD_读选通”信号, (LCD_读选通= (/12.5MHz)&(/6.25MHz) )。T1-T3由 CPU占用,在 T1-T3周期内产生相应的选通信号, (T1=(12.5MHz)&(/6.25MHz)、 T2=(/12.5MHz)&(6.25MHz)、T3=(12.5MHz)&(6.25MHz)),由于 CPU什么时间对显示缓存 RAM读写是不确定的,所以要根据 CPU的读写信号来确定 T1-T3哪个为“CPU_RAM_选通”信号(如果在 T0内来 CPU_RW则 CPU_RAM_选通=T2、T1来 CPU_RW则为 T3、T2来 CPU_RW则为 T3、T3来 CPU_RW则为 T1)。此逻辑的实现方式是,在 CPU_RW信号产生时锁存住当时的 T0-T3的状态由此来控制“CPU_RAM_选通”产生的位置。在具体时序见图 2所示。

4.2地址切换和数据分离电路的设计

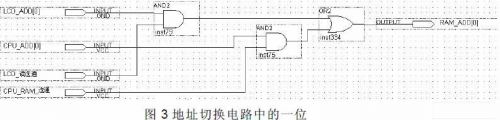

图 3是地址切换电路中的一位,以这一位为示例 ,可推出 17位地址全部电路。在图 3中 RAM_ADD=((LCD_ADD&LCD_选通)+(CPU_ADD&CPU_RAM_选通))且 “LCD_读选通”信号与“ CPU_RAM_选通”信号在任何时刻最多只能有一个是有效的,所以当“ LCD_读选通”信号与“ CPU_RAM_选通”生效时可将 RAM_ADD切换到相应的地址线上。如当某时刻“ LCD_读选通”信号与“ CPU_RAM_选通”全无效则 RAM_ADD输出应全为“ 0”。

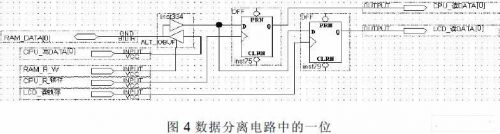

图4是数据分离电路中的一位,同样 ,以图 4这一位可推出 32位数据线。

在图 4中,RAM_R_W= (CPU_RAM_选通)&(CPU_WD),当 RAM_R_W有效时, CPU_写 DATA可通过三态门输出到 RAM_DATA上。当 CPU读 RAM时,RAM的数据由门电路输出到锁存器的输入端,在数据稳定后由“ CPU_R_锁存”信号将数据锁存在锁存器上等待 CPU将数据读走(CPU_R_锁存=(( / CPU_RD)& CPU_RAM_选通&25MHz&(/50MHz)))。

同样的在 T0周期内将 RAM的相应数据由“ LCD_锁存”信号将 32位的数据锁存在锁存器上。在相应的 T0-T3周期由 T0-T3选择相应的 8位数据输出到调色电路上,在相应时刻由 “LCD_调色输出锁存”信号将此像素点数据锁存,由 TFT_LCD读取此点的三基色数据并显示。

4.3调色电路

调色电路实际为利用 FPGA内部的片内 RAM,由 Quartus 软件生成的 24位 256字节的 RAM或 ROM,RAM或 ROM的地址线接 LCD数据锁存器的输出端后的数据选择电路,数据选择电路是将 32位的数据,按 T0-T3所决定的时间,选择相应的 8位数据。当 T0时选 D[24]-D[31]、当 T1时选 D[0]-D[7]、当 T2时选 D[8]-D[15]、当 T3时选 D[15]-D[23]。之所以将数据选择设计成 T0时选 D[24]-D[31],是因为 TFT_LCD读显示缓存 RAM时,是在 T0周期的末端才能将新数据锁存到“ LCD-读 DATA”端,新的数据只有在 T1周期才能开始显示。调色电路的输出是 3*8=24bit的本文所用的 TFT_LCD是 3*6bit的所以只用相应 8bit的低 6bit。如果将调色电路设计选择 RAM型时,可以由 CPU改写调色电路 RAM,使色彩显示更加丰富。

4.4显示缓存设计

显示缓存 RAM的选择由 LCD显示彩色多少决定的,如果显示 16色可以选择每像素点占 4bit,这样每读一次 RAM可显示 8个像素点。以此类推来选择显示缓存 RAM的大小和相应修改时序发生电路的周期。对 CPU的显示缓存 RAM口的设置时,一定要注意显示缓存 RAM的 CPU读写周期与时序发生电路的周期相一致,否则会发生读写错误。本例设置的是 160纳秒( T0+T1+T2+T3=160ns)[3,4]。

5 结束语

本文介绍了一种基于 FPGA及 NiosII软核处理器与 TFT-LCD接口的主要部分的设计要点,该设计内容已经在实际电路上得到验证,并在一些仪器的显示系统上得到应用。

关注电子行业精彩资讯,关注华强资讯官方微信,精华内容抢鲜读,还有机会获赠全年杂志

关注方法:添加好友→搜索“华强微电子”→关注

或微信“扫一扫”二维码

上一篇:一种提高遥测信号处理器测试性方法