超低功耗DDC工艺技术帮助中国IC设计业撬动IoT巨大商机

来源:华强电子网 作者:------ 时间:2015-12-25 10:49

近两年来中国IC产业势力和相关资本的几个大手笔收购事件以及IC Insight 最新榜单中两家中国大陆IC设计公司闯入全球10强,让今年的ICCAD(中国集成电路设计业2015年会暨中国集成电路产业创新发展高峰论坛)显得格外热闹和引人注目。会上,中国IC设计分会理事长魏少军公布,2015年中国IC设计产业持续扩大,销售额将达到人民币1234.16亿元,将成长25.62%,占全球IC设计产业32.39%。据中国半导体协会统计,中国IC设计公司目前统计有736家,较去年的681家扩大了55家。

中国IC设计公司成长快速的背后离不开一众IC设计服务和代工厂的推动,本届ICCAD可以说聚齐了中外IC设计服务和代工业的大半壁江山,重组一年多的富士通旗下半导体制造、测试服务公司——三重富士通半导体(MIE Fujitsu Semiconductor),以及整合了富士通和松下电器在图像、网络等应用领域LSI丰富经验和技术优势的索喜科技(Socionext)就携手亮相本届ICCAD,向新老合作伙伴展示特色超低功耗工艺和嵌入式系统代工技术优势,以及从Turn-key的Customer SoC设计到具有成本效益的COT订制的一站式服务。

在万物互联风起云涌的今天,中国IC设计公司也涌现出越来越多的玩家,进入传感器、低功耗MCU、无线连接等芯片方案领域,以追逐移动终端应用处理器之外更加广阔的市场空间,把握智能化和IoT大潮带来的更大商机。因此,在IC工艺/制程方面也从一味追逐迈向摩尔定律的更深亚微米工艺节点,转向更多讨论现有技术节点功耗降低等方面的改进上。

作为业界首家且唯一一家引进超低电压和超低漏电晶体管技术并可从事大量生产的代工企业,三重富士通半导体这次重点展示了自己开发的一系列已量产低功耗工艺技术和一项叫做“Deeply Depleted Channel(DDC)”的新工艺技术,值得广大IoT和嵌入式应用领域IC设计公司的关注,这类工艺技术甚至可以称得上是帮助IC设计公司撬动IoT亿万商机的“支点”。

业界唯一以DDC技术达到超低电压和超低漏电晶体管技术的代工厂

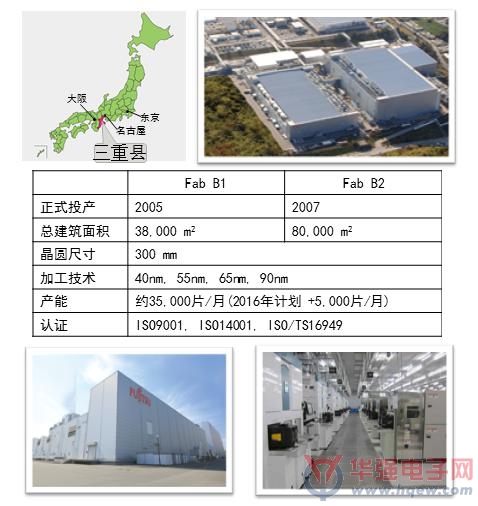

三重富士通半导体(以下简称MIFS)于2014 年12 月接管富士通半导体在三重工厂的300mm 生产线和配套设施,由此一个代工专业企业便应运而生。该公司将公司总部及市场营销的据点设在日本横滨以拓展全球性业务。

MIFS技术开发部部长仓田创在ICCAD主题演讲中表示:“顺应智能化及IoT为代表的新兴市场的增长、扩大趋势,MIFS凭借超低功耗制程和内存嵌入系统的优势强项并以配备经验丰富的工程师、不断改良生产、混合隔震建筑等高风险应对能力为基础,致力于发展为以降低功耗并控制成本为特色的代工企业,从而服务于物联社会的技术革新。”

图:三重富士通半导体技术开发部部长仓田创在ICCAD发表主题演讲。

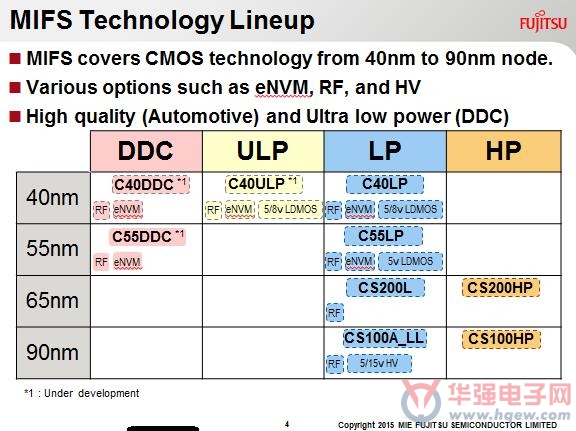

降低功耗并控制成本是IoT市场的关键,已成为半导体行业的最大课题之一,MIFS通过改善成本效率最为出色的平面CMOS工艺技术来解决这一问题。MIFS覆盖了从40-90nm节点的低功耗CMOS技术,提供eNVM、RF和HV多种选项,可支持汽车应用等高品质要求的,超级低功耗应用的DDC工艺新技术是由美国SuVolta, Inc.开发,而三重富士通半导体将制程工艺技术开发完成,并开始逐步量产,DDC具有在超低电压下可保持运作的晶体管与超低漏电晶体管技术。

独创超低功耗工艺技术——DDC解读

为了减少CMOS电力的功耗就有必要降低电源电压,而长期以来的一般做法都是采用通过晶体管微型化来实现降低电源电压。 但在90nm时代以后,由于晶体管的杂质不均引起阈值的电压不均,从而造成即使微型化也难以降低电源电压。

为实现移动穿戴设备等IoT应用不可或缺的低功耗应用,MIFS开发出DDC工艺技术。这项技术可以制造极低漏电型晶体管, 使其得以在极低Vdd下操作以实现最大的电源效率。将DDC与混合信号/RF及嵌入式NVM一起运用于40nm/55nm CMOS,不管对高度集成模拟还是对IoT/可穿戴式平台的RF SoC来说都可以实现低成本、高效用。

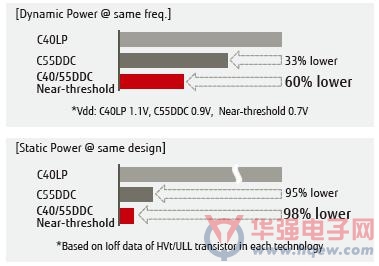

仓田创部长举例说道:“在相同的运行速度下,55nm DDC较传统55nm CMOS工艺降低了46%的总体功耗,较传统40nm工艺降低了18%。此外,超低漏电晶体管也将泄漏电流从皮安培(pA)降低到毫微微安培(fA)。”

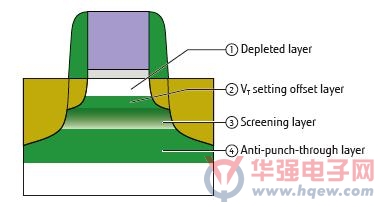

图:DDC构造。

DDC是Si基底的耗尽型沟道器件,通过简单的bulk planar工艺(平面加工工艺)制成。晶体管的通道部分由于形成多重不同浓度的杂质层,减少杂质波动这一造成阈值电压(Vth)不均的重要因素的影响,从而达到降低电源电压的目的。因采用传统的平面CMOS结构,不仅可以使用于现有的生产线装置,同时在电路设计方面也可以灵活运用现有的装置是其一大优势。

仓田创部长将DDC的主要优点归纳为以下三点:

1) 电源消耗极低:采用DDC以及降低操作电压可以实现电源总消耗的大幅度减少。

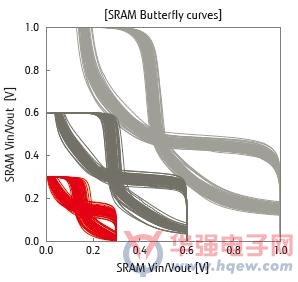

2) 降低SRAM的Vddmin:如果降低Vdd的同时增加Vt的话,SRAM的电池操作一般会变得不稳定。DDC可以实现在Vdd极低的条件下运作SRAM。即便是在Vdd=0.3V的情况下,基于DDC的SRAM蝴蝶曲线依然展现出明显的两扇窗口的模样。

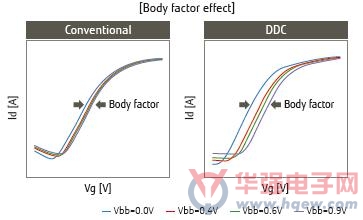

3) 强大基体因子(Body Factor)效应:DDC晶体管的body bias(Vbb)系数要强于传统的晶体管。因此,DDC可以实现Vt的灵活控制。

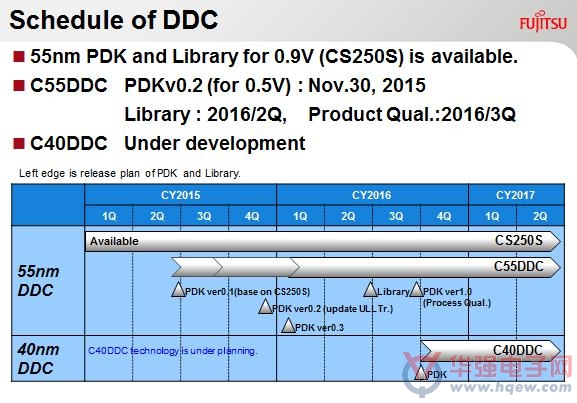

下图是三重富士通的DDC工艺发展路线图,2015年11月底该公司已开始提供PDK的“C55DDC”还可为客户量身打造提供低功耗方案,包括提供灵活的工艺优化、参数调整等服务。并且,如果客户的产品已经在别的foundry运行过,也可以到三重富士通的工厂生产,其技术人员会帮助调整参数,减少客户开发难度。

申请体验Shuttle service,降低流片成本

"Shuttle service"是指用降低芯片成本来验证客户设计的手段, 采用多项设计共享晶圆、掩模以控制成本。以下是三重富士通半导体的2016年 “Shuttle service”排期表,包括最新的55ns DDC(C55DDC)工艺技术和服务体验也将于2016的3月、6月开放,感兴趣者可提前在其官网申请。

关注电子行业精彩资讯,关注华强资讯官方微信,精华内容抢鲜读,还有机会获赠全年杂志

关注方法:添加好友→搜索“华强微电子”→关注

或微信“扫一扫”二维码

上一篇:芯片集成化中前行的自动驾驶

下一篇:符合安全设计规范的系统开发大全

- •格芯推出业界首个300mm 硅锗晶圆工艺技术2018-11-30

- •四家规模最大纯晶圆代工厂均价整体上涨 主要是得益于工艺技术的提升2018-10-15

- •江苏筹建集成电路工艺技术研究所,IC制造新模式将在南通破局?2018-08-28

- •Synopsys数字和模拟定制设计平台通过TSMC5nm工艺技术认证2018-05-25

- •“芯”势力来袭!盘点2018年市场最需要的中国芯2018-05-24

- •兆易创新预计2017年净利润达4.16亿元,同比增长136.03%2018-01-31

- •5G杀到,射频前端的需要怎样的工艺和技术?2017-05-05

- •格罗方德展示基于先进14nmFinFET工艺技术2016-12-14

- •他们助中国IC业腾飞 受到中国工程师认可2013-09-12

- •高速发展的中国IC公司面临哪些挑战?2012-09-29