基于FPGA的高速大容量FLASH存储设备设计

来源:ofweek 作者:—— 时间:2012-03-07 15:18

1、引言

用数字信号完成对数字量进行算术运算和逻辑运算的电路称为数字电路,或数字系统。由于它具有逻辑运算和逻辑处理功能,所以又称数字逻辑电路。现代的数字电路由半导体工艺制成的若干数字集成器件构造而成。逻辑门是数字逻辑电路的基本单元。存储器是用来存储二值数据的数字电路。数字电路与数字电子技术广泛的应用于电视、雷达、通信、电子计算机、自动控制、航天等科学技术各个领域。在我国20世纪90年代以前,测试系统采用磁带记录,效率和安全保障性不高;随之出现的是遥测技术,但在传输数据的过程中会出现误差;接着是静态存储器,它读、写方便,但是存储的数据会因为断电而丢失,所以,不利于数据长时间保存;目前,闪存的问世,NOR和NAND是现在市场上两种主要的非易失闪存技术,它有存储容量大、体积小、可靠性高等优点,测试系统会逐步向这个方向发展。

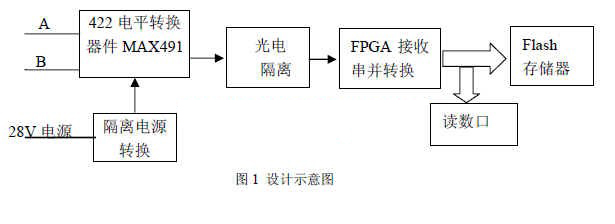

2、设计思想

2.1核心芯片选择

(1)接受芯片选择MAX491

此芯片为RS-422/485扩展芯片,为DIP14封装。MAX491有两个控制端,如果两个控制端由微处理器的一个I/O口控制,则总线,两线制,半双工工作。如果两个控制端单独控制,则总线为RS-422总线,四线制,全双工工作。MAX491采用+5V电源供电,当供电电流仅有500uA时,传输速率却能达到2.5Mbits/s.它的内部有一个传输线驱动器和一个传输线接收器,因此可以采用全双工工作。

(2)FPGA采用Spartan-II系列Xc2s100

FPGA(Field-ProgrammableGateArray),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

Spartan-II系列Xc2s100有着丰富的触发器和LUT(Look-Up-Table),非常适合复杂时序逻辑的设计。FLASH采用SAMSUNG公司的NANDflash芯片K9F8G08,接口宽度8位。每个芯片含8192个数据块,一个块分为64页,每页大小为(2K+64)Bytes,其中64Bytes为空闲区,存储容量为8Gbit.它以页为单位进行读写,以块为单位擦除、命令、数据、地址共用同一总线,具有硬件数据保护功能。

2.2MAX491设计时需要注意的问题

(1)RS-422传输线上匹配的一些说明:理论上,在每个接收数据信号的中点进行采样时,只要反射信号在开始采样时衰减到足够低就可以不考虑匹配。但这在实际上难以掌握,美国MAXIM公司有篇文章提到一条经验性的原则可以用来判断在什么样的数据速率和电缆长度时需要进行匹配:当信号的转换时间(上升或下降时间)超过电信号沿总线单向传输所需时间的3倍以上时就可以不加匹配。

一般终端匹配采用终接电阻方法,RS-422在总线电缆的远端并接电阻,终接电阻一般在RS-422网络中取100Ω,这种匹配方法简单有效,但有一个缺点,匹配电阻要消耗较大功率,对于功耗限制比较严格的系统不太适合;

另外一种比较省电的匹配方式是RC匹配;

还有一种采用二极管的匹配方法。

(2)RS-422的接地问题

RS-422四线接口由于采用单独的发送和接收通道,因此不必控制数据方向,各装置之间任何必须的信号交换均可以按软件方式(XON/XOFF握手)或硬件方式(一对单独的双绞线)。RS-422的最大传输距离为4000英尺(约1219米),最大传输速率为10Mb/s.其平衡双绞线的长度与传输速率成反比,在 100kb/s速率以下,才可能达到最大传输距离。只有在很短的距离下才能获得最高速率传输。一般100米长的双绞线上所能获得的最大传输速率仅为 1Mb/s.

RS-422需要一终接电阻,要求其阻值约等于传输电缆的特性阻抗。在短距离传输时可不需终接电阻,即一般在300米以下不需终接电阻。终接电阻接在传输电缆的最远端。

下一篇:单片机系统中的汉字显示解决方案

- •【会议议程】12月19-21日2022(十四届)传感器与MEMS产业化技术国际研讨会(暨成果展)佛山南海瞻云酒店召开2022-12-16

- •FORESEE XP1000 PCIe SSD开启Gen3后时代发展之路2021-08-02

- •FORESEE工规级SSD应用宽温技术,加速智能工业场景落地2021-07-21

- •基于J750EX测试系统的SRAM VDSR32M32测试技术研究2017-09-05

- •Vishay检查表: 采用安规电容防止过载的12点注意事项2017-07-28

- •汽车系统的USB供电2017-06-08

- •适用于 FPGA、GPU 和 ASIC 系统的电源管理2017-05-11

- •一文读懂SPI串行外设接口2017-04-27

- •TLV3501滞回比较器电路设计2017-04-14

- •ZigBee无线呼叫系统硬件电路2017-04-05