基于FPGA的高速大容量FLASH存储设备设计

来源:ofweek 作者:—— 时间:2012-03-07 15:18

RS-422标准都规定了接收器门限为±200mV.这样规定能够提供比较高的噪声抑制能力,当接收器A电平比B电平高+200mV以上时,输出为正逻辑,反之,则输出为负逻辑。但由于第三态的存在,即在主机在发端发完一个信息数据后,将总线置于第三态,这带来了一个问题:接收器输出状态不确定。如果接收机的输出为0V,网络中从机将把其解释为一个新的启动位,并试图读取后续字节,由于永远不会有停止位,产生一个帧错误结果,不再有设备请求总线,网络陷于瘫痪状态。除上述所述的总线空闲会造成两线电压差低于200mV的情况外,开路或短路时也会出现这种情况。故应采取一定的措施避免接收器处于不确定状态。

(4)RS-422的瞬态保护

由于传输线对高频信号而言就是相当于电感,因此对于高频瞬态干扰,接地线实际等同于开路。这样的瞬态干扰虽然持续时间短暂,但可能会有成百上千伏的电压。实际应用环境下还是存在高频瞬态干扰的可能。一般在切换大功率感性负载如电机、变压器、继电器等或闪电过程中都会产生幅度很高的瞬态干扰,如果不加以适当防护就会损坏RS-422通信接口,对于这种瞬态干扰可以采用隔离或旁路的方法加以防护。方法有隔离保护方法和旁路保护方法。

2.3FPGA内部编程设计

采用MAX491串行接收实时数据,并通过Xc2s100串行数据转换为并行数据,并控制存储到Flash中,在这个过程中,最关键的是对Spartan-II系列Xc2s100内部编程,内部模块包括异步串行通信模块和控制FLASH存储、读数和擦除模块。

flash的英文解释为:n.闪光,闪现,一瞬间,闪现,反射,使迅速传便,vt.使闪光,反射adj.闪光的,火速的。Flash也是由macromedia公司推出的交互式矢量图和Web动画的标准,由Adobe公司收购。网页设计者使用Flash创作出既漂亮又可改变尺寸的导航界面以及其他奇特的效果。Flash也是存储芯片的一种,通过特定的程序可以修改里面的数据。

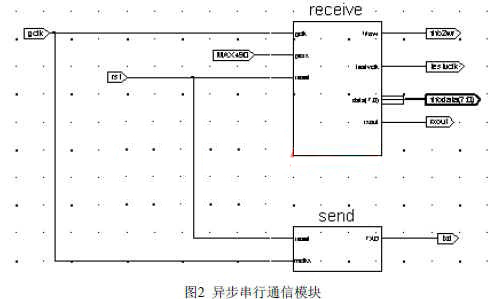

(1)异步串行通信模块(如图2)UART发送模块(如图2中的send)发送器每隔16个CLK16时钟周期输出1位,次序遵循1位起始位、8位数据位(假定数据位为8位)、1位校验位(可选)、1位停止位;

何时通过UART发送数据由CPU控制,也就是说CPU要接受数据必须判断当前是否可写,如果不判这个条件,接受的数据会出错。

数据的发送是由微处理器控制,微处理器给出信号,发送模块根据此信号将并行

数据din[70]通过移位寄存器转换为串行数据至串行数据输出端Txd.UART接收模块(如图2中的receive)

串行数据帧和接收时钟是异步的,发送来的数据由逻辑?1‘变为逻辑’0‘可以视为一个数据帧的开始。

接收器先要捕捉起始位,确定rxd输入由1到0,逻辑0需要8个CLK16时钟周期,才是正常的起始位,然后在每隔16个CLK16时钟周期采样接收数据(也可以为其它数),将串行数据din通过移位寄存器发送串行数据至并行数据输出端dout[70],放入存储器件。在数据发送过程中用输出信号fifowr作为标志信号,当一帧数据发送完毕时,fifowr信号为0,通知CPU在下个时钟装入新数据。

下一篇:单片机系统中的汉字显示解决方案

- •【会议议程】12月19-21日2022(十四届)传感器与MEMS产业化技术国际研讨会(暨成果展)佛山南海瞻云酒店召开2022-12-16

- •FORESEE XP1000 PCIe SSD开启Gen3后时代发展之路2021-08-02

- •FORESEE工规级SSD应用宽温技术,加速智能工业场景落地2021-07-21

- •基于J750EX测试系统的SRAM VDSR32M32测试技术研究2017-09-05

- •Vishay检查表: 采用安规电容防止过载的12点注意事项2017-07-28

- •汽车系统的USB供电2017-06-08

- •适用于 FPGA、GPU 和 ASIC 系统的电源管理2017-05-11

- •一文读懂SPI串行外设接口2017-04-27

- •TLV3501滞回比较器电路设计2017-04-14

- •ZigBee无线呼叫系统硬件电路2017-04-05