Vishay P沟道Gen III MOSFET具有业内最低导通电阻

来源:华强电子网 作者:—— 时间:2013-12-03 09:24

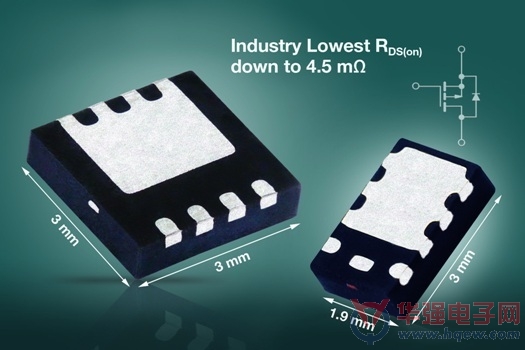

日前,Vishay宣布,推出采用PowerPAK? ChipFET?和PowerPAK 1212-8S封装的新器件,扩充其TrenchFET? P沟道Gen III功率MOSFET。今天推出的Vishay Siliconix MOSFET可提高便携式计算和工业控制设备中的电源效率,是-4.5V和-2.5V栅极驱动下具有业内最低导通电阻的-12V和-20V器件,占位面积为3.0mm x 1.9mm x 3.3mm。

Si5411EDU、Si5415AEDU和SiSS23DN适用于智能手机、平板电脑、笔记本电脑、工业传感器和POL模块里的电源管理等各种应用中的负载、电池和监控开关。器件的低导通电阻使设计者能够在其电路里实现更低的电压降,更高效地使用电能,延长电池使用寿命。

在节省PCB空间是首要因素的应用里,-12V Si5411EDU不但具有8.2mΩ(-4.5V)和11.7mΩ(-2.5V)低导通电阻,而且3.0mm x 1.9mm PowerPAK ChipFET封装具有明显优势。当需要更高的电压等级时,-20 V Si5415AEDU可满足需求,具有9.6mΩ(-4.5V)和13.2mΩ(-2.5V)的低导通电阻。两款器件的典型ESD保护为5000V。对于需要极低导通电阻的应用,SiSS23DN的4.5m?(-4.5V)和6.3m?(-2.5V)导通电阻可满足需求,3.3mm x 3.3 mm PowerPAK 1212-8S封装的高度低至0.75mm。

Si5411EDU、Si5415AEDU和SiSS23DN进行了100%的Rg和UIS测试。这些MOSFET符合JEDEC JS709A的无卤素规定,符合RoHS指令2011/65/EU。

器件规格表:

|

器件型号 |

Si5411EDU |

Si5415AEDU |

SiSS23DN | |

|

VDS (V) |

-12 |

-20 |

-20 | |

|

VGS (V) |

± 8 |

± 8 |

± 8 | |

|

RDS(ON) (m?) @ |

4.5 V |

8.2 |

9.6 |

4.5 |

|

3.7 V |

9.4 |

- |

- | |

|

2.5 V |

11.7 |

13.2 |

6.3 | |

|

1.8 V |

20.6 |

22.0 |

11.5 | |

|

封装 |

PowerPAK ChipFET |

PowerPAK ChipFET |

PowerPAK 1212-8S | |

Vishay的P沟道Gen III系列包括60余款器件,占位面积从5mm x 6mm到0.8mm x 0.8mm。

新款P沟道MOSFET现可提供样品,并已实现量产,大宗订货的供货周期为十三周。

- •更新探头优化性能,Flir VS80内窥镜适配狭窄区域检测的多元需求!2025-11-25

- •塔克热系统MBX系列微型热电制冷器赋能AI数据中心下一代可插拔设备2025-11-21

- •极小尺寸——吾爱易达推出高集成度芯片级LTE Cat1模组SCS527E2025-08-20

- •广和通发布5G AI MiFi 解决方案,重新定义AI智联万物2025-05-22

- •东芝推出带有嵌入式微控制器的SmartMCD系列栅极驱动IC2024-03-28

- •Melexis推出动态RGB-LED应用新型开发方案2024-03-27

- •瑞萨率先在业内推出采用自研CPU内核的通用32位RISC-V MCU2024-03-26

- •东芝推出适用于电机控制的Arm Cortex-M4微控制器2024-03-26

- •艾迈斯欧司朗LED产品搭配二维码(Data Matrix)技术,帮助汽车制造商简化生产流程2024-03-25

- •颠覆性 Cadence Reality 数字孪生平台为人工智能时代的数据中心设计带来变革2024-03-22