基于FPGA高速大容量数据采集与存储系统

来源:华强电子网 作者:------ 时间:2014-07-11 14:17

2硬件设计

系统的硬件由模数转换电路、数据采集存储与传输控制电路、接口电路构成。

2.1模数转换电路设计

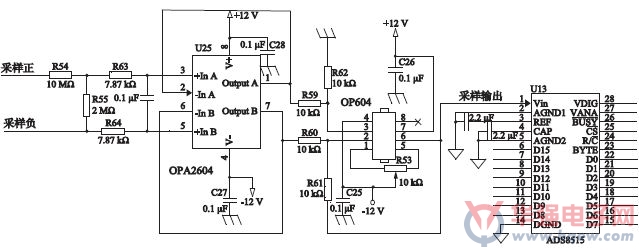

模数转换电路是整个系统的重要组成部分,它由差分放大适配电路、A/D转换器构成,如图1所示,其核心器件是A/D转换芯片ADS8515。

图1 信号适配和模数转换电路原理图

模拟输入信号经过由OPA2604和OP604构成的差分放大适配电路将信号适配到ADS8515的采集范围。ADS8515将模拟信号转换为数字信号。ADS8515的控制信号由FPGA提供,ADS8515在控制信号的作用下,以适当的时序完成转换工作。

2.2数据采集存储与传输控制电路设计

数据采集存储与传输控制电路的开发工作主要集中在FPGA上。FPGA负责在CF卡与A/D芯片之间的缓冲与控制,一边与A/D接口,另一边与CF卡接口,产生数据采集、A/D转换、FIFO所需的全部控制信号,实现对传输数据的缓存、读/写控制、时钟、输出使能以及对A/D的控制等功能。

2.2.1FPGA内部总体设计

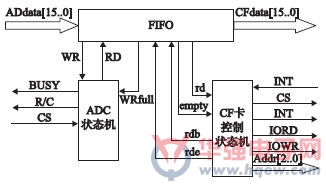

FPGA设计内部结构简图如图2所示,由FIFO、CF卡控制状态机、ADC接口控制状态机三部分构成。

图中由左向右的宽箭头表示数据流,ADdata[15..0]是与A/D转换连接的数据总线,CFdata[15:0]是与CF卡连接的数据总线。单线箭头表示输入输出及FPGA内部各个模块间的控制信号线。从数据流向看,数据在ADC接口控制状态机的协调下通过ADC接口送入FIFO中,经过FIFO的缓冲后,在CF卡控制状态机的协调下,数据传输存储到CF卡;当CF卡存储满时,FPGA通过ADC状态机停止A/D的采集,并提示用户更换CF卡。

2.2.2数据双缓存器FIFO

由于与CF卡接口的数据传输方式是突发的数据块传送,每个数据块是用很高的速率传送到CF卡,这样就必须有缓存把A/D采集来的数据先缓存,然后发送到CF卡进行存储。然而FPGA内部的FIFO不足以支持系统中大量数据的暂时存储,这就要求很大的中间缓存。在本系统中利用FPGA对外部SDRAM的控制,以达到大量高速存取数据的功能。SDRAM选用MICRON公司的MT48LC4M32B2,存储容量为128MB,数据带宽为32位,内部由4个BANK组成,每个BANK有4096行和256列。

图2 数据采集与传输控制结构示意图

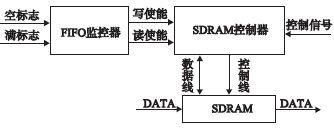

本文设计的FIFO系统由FPGA和SDRAM两部分组成。其中FPGA内部包含FIFO监控器、缓冲器、SDRAM控制器三个模块。FIFO监控器的作用是将SDRAM的状态转变成SDRAM控制器的读、写信号。若操作为向SDRAM写数据,则在SDRAM满时,FIFO监控器送出一个信号,以阻止写操作继续向SDRAM中写数据而造成溢出;若操作为向SDRAM读数据,则在缓冲器已空时,FIFO监控器送出一个信号,以阻止读操作继续从SDRAM中读数据而造成无效数据的读出。FIFO系统的模块结构如图3所示。

图3 FIFO模块结构示意图

- •兆易创新GD25UF系列容量全线扩展:以1.2V超低功耗存储赋能AI计算2026-03-11

- •涨价100%!存储巨头再传重磅信号2026-01-26

- •最新全球存储厂商业绩PK及涨价原因分析2025-11-13

- •又一芯片加入存储涨价阵营!2023-12-26

- •突发!Marvell再裁员!2023-11-17

- •全球存储厂商最新业绩大PK2023-11-10

- •主打高阶市场!这家厂商引领定制化存储行业发展2023-05-31

- •韩国发芯片发展十年蓝图,确保存储及代工的“超级差距”2023-05-10

- •存储巨头美光拒绝5月再降价2023-04-27

- •CFMS 2017峰会:一场超越行业期望的存储界盛会2017-09-08