基于可调节输出低压差稳压器的降噪网络设计

来源:华强电子网 作者:------- 时间:2014-08-14 10:38

简介

低压差稳压器 (LDO)可用来为高速时钟、模数转换器、数模转换器、压控振荡器和锁相环这些电路供电。噪声对于高性能模拟电路的设计人员而言极为重要。降低噪声的关键是保持LDO噪声增益接近单位增益,且不影响交流性能或直流闭环增益。

本文描述简单的RC网络如何降低可调节输出低压差稳压器的输出噪声。本文通过实验数据来演示这一简单方法的有效性。虽然RC网络的主要目的是降噪,但它也能改善电源抑制和负载瞬态响应。

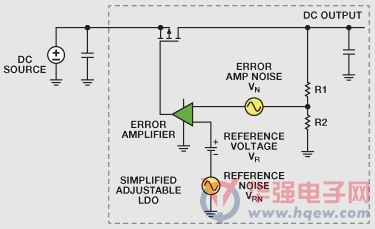

图 1 显示典型可调节输出LDO的简化框图。输出电压VOUT等于基准电压与误差放大器直流闭环增益的乘积:VOUT = VR × (1 + R1/R2),其中(1 + R1/R2)是误差放大器的直流闭环增益。

误差放大器噪声VN和基准电压噪声VRN放大相同的倍数,使输出噪声与设定的输出电压成比例增加。这使得输出电压上的噪声比参考电压高但小于 2 倍,输出噪声适度增加但在敏感应用 中哪怕这种适度增加都有可能无法接受。

图 1. 显示内部噪声源的可调节 LDO 简化框图

LDO 噪声

LDO的主要噪声源是内部基准电压和误差放大器。当今的器件工作时内部偏置电流为几百nA或更低,可实现高达 15 μA的静态电流。这些小电流需要使用高达 1 GΩ的偏置电阻,使得误差放大器和基准电压电路相比分立式部署更为噪杂。典型LDO采用电阻分压器设置输出电压,因此噪声增益等于交流闭环增益,其结果与直流闭环增益相同。

降低 LDO 噪声

两种降低LDO噪声的主要方法是过滤基准电压,以及降低误差放大器的噪声增益。某些LDO可采用外部电容过滤基准电压。事实上,许多所谓的超低噪声LDO都需要使用外部降噪电容来实现其低噪声性能。这项技术的缺点是误差放大器噪声和任何残留的基准电压噪声依然会通过交流闭环增益放大。这使得噪声与输出电压成正比。

降低误差放大器的噪声增益可使LDO的输出噪声不随输出电压上升而大幅增加。不幸的是,这对于固定输出LDO而言是不可行的,因为反馈节点不易获得。然而幸运的是,该节点在可调节输出LDO中容易获得。

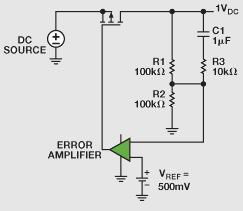

图 2 显示的是一个可调节输出LDO,其中R1 和R2 设置输出电压。由R3 和C1 构成的网络可降低误差放大器的交流增益。为确保具有低相位裕量(或者非单位增益稳定)LDO的稳定性,选择R3 将放大器的高频增益设为 1.1 左右。如需降低 1/f区的噪声,则需选择C1 将低频零点设为 10 Hz以下。

图 2. 降低可调节输出 LDO 噪声增益的简单 RC 网络

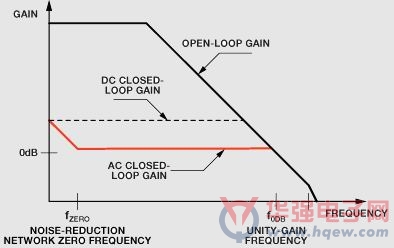

图 3 将交流闭环增益(其降噪网络经过适当设计)与开环增益 以及未经过修改的闭环增益进行比较。采用降噪网络后,在大 部分带宽中交流增益接近单位增益,因此基准电压噪声和误差 放大器噪声放大的程度较低。

图 3. LDO 环路增益与频率的关系(带降噪网络

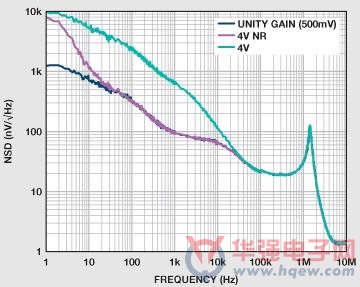

图 4 显示降噪网络对ADP125 LDO噪声谱密度的影响。该曲线比较了使用和不使用降噪网络时,4 V电压下的噪声谱密度,以及单位增益下的噪声谱密度。

图 4. 可调节输出 LDO ADP125 的噪声谱密度

可看到在 20 Hz至 2 kHz范围内,噪声性能得到了极大的改善。在R1 和C1 组成的零点之上,采用降噪网络的噪声特性与单位 增益时基本相同。噪声谱密度曲线在 20 kHz以上融合,这是因为误差放大器的闭环增益与开环增益相交,无法进一步降低噪声增益。

电源抑制

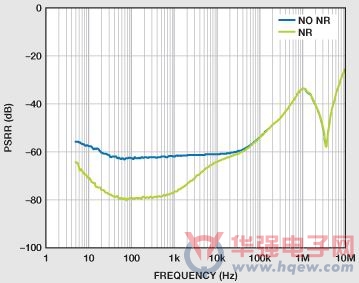

此频率范围内的电源抑制比(PSRR)同样得到了改善。PSRR衡量电路抑制电源输入端出现的外来信号(噪声和纹波),使这些 干扰信号不至于破坏电路输出的能力。PSRR定义为:PSRR = VEIN/VEOUT。这还可以用dB表示:PSR = 20 × log(VEIN/VEOUT), 其中VEIN 和VEOUT 为出现在输入端和输出端的外来信号。

对于大部分模拟电路,PSR用于为电路内部供电的引脚。然而,对于LDO,输入引脚不仅为内部电路供电,还为稳压输出提供负载电流。

改善 PSR

使用降噪网络降低可调节输出LDO输出噪声还有另一个优势,即还能改善低频PSR。图 2 中的R1、R3 和C1 形成超前-滞后网络,其零点大致在 1/(R1 × C1)处,极点大致在 1/(R3 × C1)处。超前-滞后网络为补偿环路提供正馈功能,因此能改善PSR。对于低于闭环增益和开环增益融合的频率而言,若改善的量以dB表示,则数值约为 20 × log(1 + R1/R3)。

图 5 显示降噪网络对可调节输出LDO ADP7102 所产生的影响。若输出为 9 V,则R1 = 64 kΩ、R2 = 10 kΩ、R3 = 1 kΩ、C1 = 1 μF。R1 和C1 在大约 2.5 Hz时建立的零点证明 10 Hz以上PSRR得到了改善。在 100 Hz至 1 kHz范围内,总PSRR增加约 17 dB。改善情况直到约 20 kHz处才有所下降;在该处,开环增益和闭环增益融合。

图 5. 使用和不使用降噪网络的可调节输出 LDO

ADP7102/ADP7104 的 PSRR

瞬态负载改善

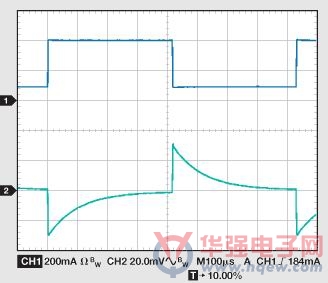

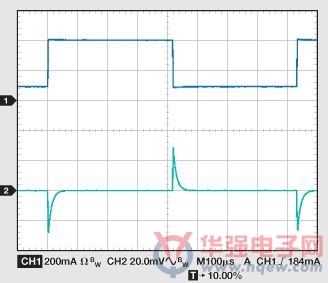

降噪网络还能改善LDO的瞬态负载响应。同样,R1、R3 和C1执行补偿环路的前馈功能。负载瞬态的高频分量——由未经衰减的误差放大器检测——允许误差放大器快速响应负载瞬态。图 6 显示使用与不使用降噪网络时的ADP125 负载瞬态响应情况。使用降噪网络后,LDO能在 50 μs内响应负载瞬态,而不使用降噪网络时为 500 μs。

图 6. 可调节输出 LDO ADP125 的瞬态负载响应

(a) 不使用降噪网络 (b) 使用降噪网络

图 6. 可调节输出 LDO ADP125 的瞬态负载响应

(a) 不使用降噪网络 (b) 使用降噪网络

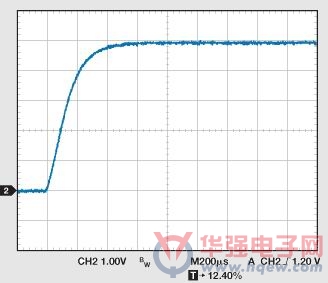

对启动时间的影响

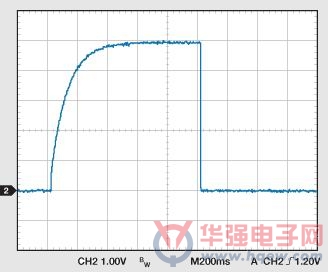

降噪网络的一个缺点是它会极大地增加启动时间。图 7 显示使用与不使用降噪网络时的ADP125 启动时间。正常启动时间约为 600 μs。若C1 = 10 nF,则启动时间增至 6 ms;若C1 = 1 μF,则增至 600 ms。对于电路完全上电后不再开关LDO的应用而言,启动时间增加应该不是问题。

图 7. 可调节输出 LDO ADP125 的启动时间

(a) 不使用降噪网络 (b) 使用降噪网络,C1 = 10 nF

(c) 使用降噪网络,C1 = 1 μF

结论

通过添加一个简单的RC降噪网络,便可明显改善可调节输出LDO的噪声、电源抑制和瞬态性能,为高速时钟、模数转换器、数模转换器、压控振荡器和锁相环等噪声敏感型应用带来极大的优势。

ADP125、ADP171、ADP1741、ADP1753、ADP1755、ADP7102、ADP7104和ADP7105 等LDO均具有这种通用架构,并将极大 地受益于降噪网络的使用。该技巧可用于与图 2 所示相似的 LDO架构,在该架构中,基准电压噪声和误差放大器噪声均由 直流闭环增益放大,因此输出噪声与输出电压成比例关系。

较新的超低噪声LDO——比如 ADM7151 ——不会得益于此降 噪网络,因为该架构采用单位增益LDO误差放大器,所以基准电压等于输出电压。此外,内部基准电压滤波器极点低于 1 Hz,可极大地过滤基准电压,并消除几乎全部基准电压噪声影响。

关注电子行业精彩资讯,关注华强资讯官方微信,精华内容抢鲜读,还有机会获赠全年杂志。

关注方法:添加好友→搜索“华强微电子”→关注

或微信“扫一扫”二维码