力科推出简单易用的DDR信号调试工具-DDR Debug toolkit

来源:互联网 作者:------- 时间:2014-12-29 10:22

引论

现在示波器上的DDR物理层信号分析方案,都是针对JEDEC规范的一致性测试。在这种方案中,分析软件会按照 JEDEC规范分析DDR信号的各种参数,并判断测试结果Pass或者Fail,最终生成一份报告。但是很多的研发工程师,并不想仅仅获得一个Pass或者Fail的结果,而是想对信号做调试分析,但是传统的串行信号分析软件无法分析DDR信号,为此,力科推出了新的DDR Debug toolkit。

新的DDR信号分析方法

力科DDR Debug toolkit提供了一种简单易用的DDR信号调试工具,它快速的对数据做读写分离,形成读写眼图,对眼图进行模板测试和参数测试,对抖动进行分解,定位问题的根源,对比较重要DDR参数进行测量,像建立时间、保持时间、TDQSCK 等,灵活设置参数,对 DDR 信号问题进行调试,可以支持DDR2/DDR3/DDR4/LPDDR2/LPDDR3等。

快速对 DDR 信号进行读写分离

一键对DDR信号进行读写分离,简化了分离步骤,节省了时间,在此基础上,就可以对信号进行测量分析。

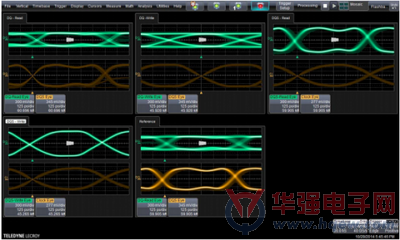

眼图测量

可以同时产生和显示10个眼图,对5路DDR信号进行分析,查看分析眼间的Skew和时间信息,可以选择DQS或者Clock作为时间参考,自定眼图模板,进行眼图模板测试。

测量多个眼图参数:

Eye Height/Eye Width/Eye Crossing/Mask Hits/Mask Out/Eye Amplitude/One Level/Zero Level

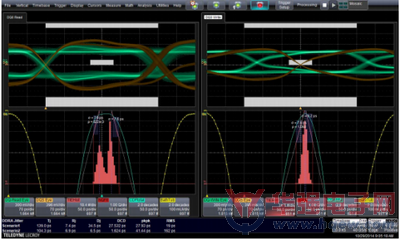

抖动测试

像传统的串行信号分析一样,对DDR信号的抖动进行测量分析,对抖动进行分解(Tj,Rj,Dj,DCD等),从TIE Track、TIE Histogram、Bathbub Curve观察分析抖动,更加深入的了解抖动的分布和源头。

DDR 参数测量

对比较关键的DDR参数进行测量,可以同时测量12个参数,包括Max、Min,Mean等统计值。

Bursts,transitions,Vref

VH(ac),VH(dc),VL(ac),VL(dc)

tDS,tDH,tIS,tIH

tDQSQ,tDQSCK

Slew Rise,Slew Fall

关注电子行业精彩资讯,关注华强资讯官方微信,精华内容抢鲜读,还有机会获赠全年杂志

关注方法:添加好友→搜索“华强微电子”→关注

或微信“扫一扫”二维码

- •更新探头优化性能,Flir VS80内窥镜适配狭窄区域检测的多元需求!2025-11-25

- •塔克热系统MBX系列微型热电制冷器赋能AI数据中心下一代可插拔设备2025-11-21

- •极小尺寸——吾爱易达推出高集成度芯片级LTE Cat1模组SCS527E2025-08-20

- •广和通发布5G AI MiFi 解决方案,重新定义AI智联万物2025-05-22

- •东芝推出带有嵌入式微控制器的SmartMCD系列栅极驱动IC2024-03-28

- •Melexis推出动态RGB-LED应用新型开发方案2024-03-27

- •瑞萨率先在业内推出采用自研CPU内核的通用32位RISC-V MCU2024-03-26

- •东芝推出适用于电机控制的Arm Cortex-M4微控制器2024-03-26

- •艾迈斯欧司朗LED产品搭配二维码(Data Matrix)技术,帮助汽车制造商简化生产流程2024-03-25

- •颠覆性 Cadence Reality 数字孪生平台为人工智能时代的数据中心设计带来变革2024-03-22