详解全球首款eFPGA:模块化设计如何实现功耗和性能最佳平衡点

FPGA作为专用集成电路(ASIC)领域中的一种半定制电路而出现的产物,目前正在经历第三个发展阶段,市场容量也在加速提升。从ASIC的发展历史来看,ASIC集成了越来越多的IP功能,但FPGA因为技术工艺门槛太高,技术研发成本太贵,一直没有半导体厂商将其作为一个IP集成到ASIC,而这一点正因Achronix半导体公司发生改变。

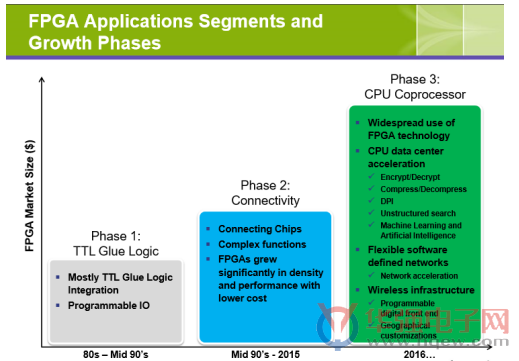

Achronix半导体公司CEO Robert Blake日前在接受华强电子网等媒体专访时称,FPGA第一个阶段主要用于实现TTL胶合逻辑,市场总量在5亿美元左右;第二个阶段是互联网时代,FPGA被用于在路由器/交换机中做ASIC连接,市场容量也由5亿美元增长到50亿美元。

全球首款eFPGA上市 接口带宽比FPGA超10倍

“如今FPGA正在第三个发展阶段,其增长将由CPU协处理器来主导,其主要应用包括:CPU数据中心加速,软件定义网络(SDN),以及将包括5G在内的移动通信等,市场容量将会大幅提升。为此,Achronix在经过三年的开发后,推出了可集成至客户系统级芯片(SoC)中的Speedcore嵌入式FPGA(embedded FPGA,eFPGA)IP产品,并已开始向客户供货。”Robert Blake如是说。

Achronix公司CEO Robert Blake(左)和Achronix公司亚太区总经理罗炜亮(右)

据了解, Achronix发布的Speedcore eFPGA技术是专为计算和网络加速应用而设计,采用英特尔22nm工艺,Speedcore eFPGA产品是使用Achronix成熟的、经过验证的ACE软件设计工具,其是将FPGA作为IP嵌入到SoC内,帮助SoC来做加速和数据处理。

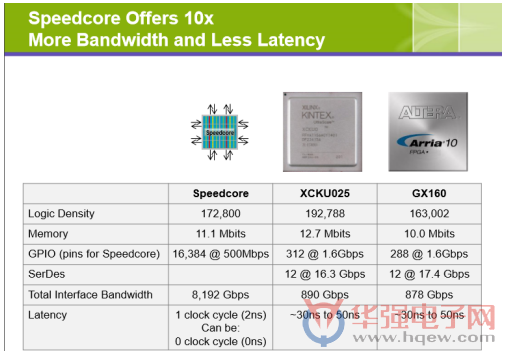

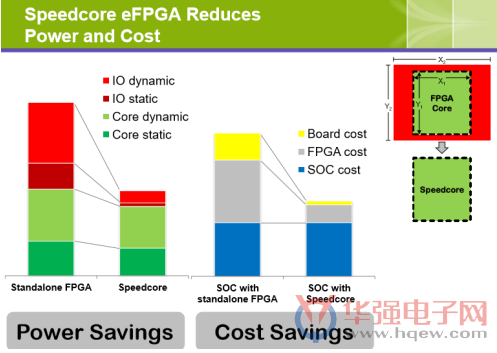

Speedcore eFPGA IP产品是一款高端FPGA内核,具体而言,与独立的FPGA相比有哪些应用优势?Robert Blake告诉记者,具备FPGA灵活性的同时,与FPGA器件相比,其显著优势包括:互联带宽增加10倍,互联延迟减小至1/10,功耗降低50%,成本降低90%。

与竞争对手Xilinx和Altera 的独立FPGA(Xilinx XCKU025、Altera GX160)相比,eFPGA可以实现超过10倍接口带宽。

Robert Blake表示:“多年以来,不同的公司都一直在谈论eFPGA产品,但Achronix的Speedcore是首款向客户出货的eFPGA IP产品,它是游戏规则的改变者。Achronix曾是第一家提供带有嵌入式系统级别IP的高密度FPGA的供应商。我们正在使用相同的、经过验证的技术向客户提供我们的eFPGA产品,这些客户都希望将ASIC设计的各种高效能和eFPGA可编程硬件加速器的灵活性结合在同一款芯片中。”

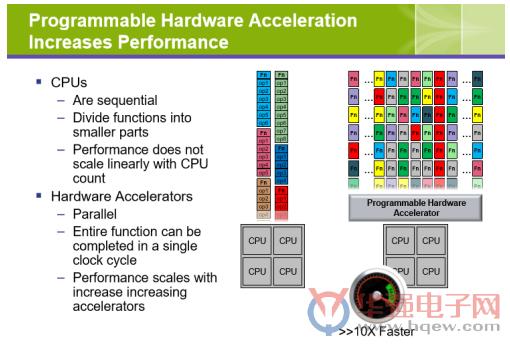

目前,FPGA在系统级芯片中的应用占比并不大,但随着多核CPU处理的数据越来越大以及未来5G的到来,嵌入式的FPGA在CPU中的应用将会提升。相比之下,将eFPGA嵌入到SoC中与CPU连接,能够帮助CPU并行处理多个业务,带来处理性能的提升也更为明显。

嵌入SoC成本优势明显 模块化可达功耗和性能最佳平衡点

传统的多核CPU和SoC需要可编程硬件加速器来预处理和卸载数据,从而提升其计算性能。FPGA是最佳的硬件加速器解决方案,因为随着算法的不断变化,加速器需要不断用新的功能来实现更新,Achronix通过ACE软件设计工具,可以快速改进Speedcore eFPGA IP产品应用。

Achronix的eFPGA IP产品在设计上内嵌到SoC

在设计上,eFPGA通过内嵌到SoC中,接口将会非常简单,处理延迟方面可以大幅减少——2ns或0ns,可以省去周边逻辑(IO)和外围元器件,降低功耗的同时,可以更好地保障信号完整性。

在成本上,如果购买独立外挂的FPGA,其成本是很高的,而eFPGA通过其特有设计在省去周边逻辑器件的同时,电路板的面积与层数也会减少,成本优势更为明显。

那么Achronix的eFPGA是如何交付到客户手中?Robert Blake告诉记者,Achronix会根据客户的需求提供汇编工具和软件,进行定制化的方式来方便客户开发。

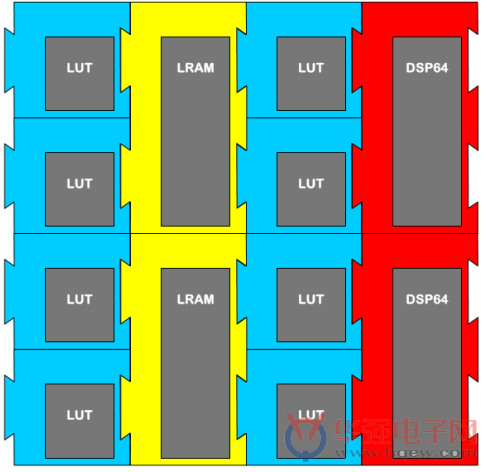

Speedcore eFPGA所有资源都采用模块化设计

“我们定制的是模块化,不同的资源、逻辑、存储器的IP都是模块化,根据客户定制化的需要,我们可以快速集成在一起。”Robert Blake表示,如果客户有不同的需求要不同的资源,可以根据需求拼出新的核。比如5G的客户需要更多的DSP处理,如果要做高端性能计算,可以增加更多的存储器。

除了IP可以定制化,工艺制程也可以定制。“比如客户更高需求,我们可以基于台积电的16nm工艺来做。如果客户说需要新的工艺,比如Intel的22nm工艺,我们大概需要4~6个月来进行转移。”目前已经可以提供基于台积电(TSMC)的16纳米FinFET Plus(16FF+)工艺的Speedcore IP产品,并且正在开发基于台积电的7纳米工艺的IP。

据了解,Achronix是目前唯一能提供独立的FPGA和EFPGA的半导体公司,其商业模式与ARM类似。客户可以针对其应用来定制最佳的芯片面积、功耗和资源配置,可以定义查找表(LUT)、嵌入式存储器以及DSP的数量。此外,客户可以定义Speedcore的宽高比、输入输出(IO)端口的连接,还可以在功耗和性能之间进行权衡,为其实现从处理器卸载那些高密度计算任务到eFPGA IP中,从而带来显著的性能提升。(责编:宏达)

本文为华强电子网原创,版权所有,转载需注明出处

关注电子行业精彩资讯,关注华强资讯官方微信,精华内容抢鲜读,还有机会获赠全年杂志

关注方法:添加好友→搜索“华强微电子”→关注

或微信“扫一扫”二维码

- •瑞萨电子推出全新低功耗蓝牙SoC,为车载应用带来更低能耗2025-03-27

- •Conformal AI Studio 可将 SoC 设计师的效率提升 10 倍2025-03-20

- •Honda(本田)与瑞萨签署协议, 共同开发用于软件定义汽车的高性能SoC2025-01-08

- •瑞萨推出高能效第四代R-Car车用SoC引领ADAS产品创新2024-09-24

- •旋智科技重磅发布“高度集成的片上系统(SoC)微控制器SPD1179”!2023-03-29

- •字节跳动招募SoC设计/验证人才2022-06-14

- •比科奇与Radisys联合验证5G Open RAN系统级芯片(SoC), 实现系统集成的里程碑2022-05-23

- •创新无界,汇顶科技启航IoT全场景应用 —— 2022汇顶科技创新技术研讨会开幕2022-05-19

- •中国智能机SoC排名:2月联发科稳居第一,高通占比回升2022-03-31

- •Imagination和瑞昱半导体携手推出全球首款具有图像压缩功能的 数字电视SoC2022-03-11