Intel公开三项全新封装技术:灵活、高能集成多芯片

在本周旧金山举办的SEMICON West大会上,Intel介绍了三项全新的先进芯片封装技术,并推出了一系列全新基础工具,包括EMIB、Foveros技术相结合的创新应用,新的全方位互连(ODI)技术等。

作为芯片制造过程的最后一步,封装在电子供应链中看似不起眼,却一直发挥着极为关键的作用。作为处理器和主板之间的物理接口,封装为芯片的电信号和电源提供着陆,尤其随着行业的进步和变化,先进封装的作用越来越凸显。

另一方面,半导体工艺和芯片架构的日益复杂,传统SoC二维单芯片思路已经逐渐行不通,chiplet多个小芯片封装成为大势所趋。

Intel正是利用先进技术,将芯片和小芯片封装在一起,达到SoC的性能,而异构集成技术提供了前所未有的灵活性,能够混搭各种IP和工艺、不同的内存和I/O单元,Intel的垂直集成结构在异构集成时代尤其独具优势。

Intel此次公布的三项全新封装技术分别是:

一、Co-EMIB

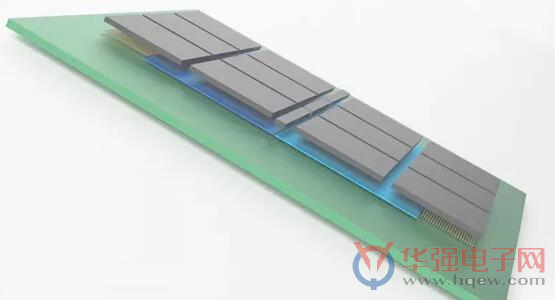

利用利用高密度的互连技术,将EMIB(嵌入式多芯片互连桥接) 2D封装和Foveros 3D封装技术结合在一起,实现高带宽、低功耗,以及相当有竞争力的I/O密度。

Co-EMIB能连接更高的计算性能和能力,让两个或多个Foveros元件互连从而基本达到SoC性能,还能以非常高的带宽和非常低的功耗连接模拟器、内存和其他模块。

Foveros 3D封装是Intel在今年初的CES上提出的全新技术,首次为CPU处理器引入3D堆叠设计,可以实现芯片上堆叠芯片,而且能整合不同工艺、结构、用途的芯片,相关产品将从2019年下半年开始陆续推出。

二、ODI

ODI全程Omni-Directional Interconnect,也就是全方位互连技术,为封装中小芯片之间的全方位互连通信提供了更大的灵活性。

ODI封装架构中,顶部的芯片可以像EMIB下一样,与其他小芯片进行水平通信,还可以像Foveros下一样,通过硅通孔(TSV)与下面的底部裸片进行垂直通信。

ODI利用更大的垂直通孔,直接从封装基板向顶部裸片供电,比传统硅通孔更大、电阻更低,因而可提供更稳定的电力传输,同时通过堆叠实现更高的带宽和更低的时延。

此外,这种方法减少了基底芯片所需的硅通孔数量,为有源晶体管释放更多的面积,并优化了裸片的尺寸。

三、MDIO

基于高级接口总线(AIB)物理层互连技术,Intel发布了这种名为MDIO的全新裸片间接口技术。

MDIO技术支持对小芯片IP模块库的模块化系统设计,能效更高,响应速度和带宽密度可以是AIB技术的两倍以上。

Intel强调,这些全新封装技术将与Intel的制程工艺相结合,成为芯片架构师的创意调色板,自由设计创新产品。

关注电子行业精彩资讯,关注华强资讯官方微信,精华内容抢鲜读,还有机会获赠全年杂志

关注方法:添加好友→搜索“华强微电子”→关注

或微信“扫一扫”二维码

- •密集谈判一年多,苹果公司与英特尔达成协议,后者将为苹果设备生产芯片2026-05-12

- •巨头退场!三星宣布在中国大陆停售家电产品:手机业务不受影响 仍正常销售2026-05-12

- •2026“瑞萨杯”信息科技前沿专题赛决赛开赛2026-05-12

- •氮化镓+MCU赋能高效OBC:大联大诠鼎与英飞凌共探车载电源新趋势2026-05-12

- •护航企业合规出海,大联大世平携手VicOne成功举办CRA网络安全实践研讨会2026-05-12

- •摩尔斯微电子与得捷电子合作,扩展Wi-Fi HaLow解决方案全球供应范围2026-05-12

- •份额腰斩!暴跌 29.5%!Infineon财报撕烂车规巨头体面2026-05-09

- •摩尔斯微电子选定Gateworks作为首个全球设计合作伙伴2026-05-08

- •东芝发布支持PCIe 6.0与USB4 2.0版等高速差分信号的2:1多路复用器/1:2解复用器开关2026-05-07

- •大联大世平北京车展首秀,携手安森美(onsemi)等伙伴展现车载电子系统整合实力2026-05-07