Intel台积电ASML齐捧EUV光刻 突破摩尔定律瓶颈的关键因素之一

日前,中国国际半导体技术大会(CSTIC)在上海开幕,为期19天,本次会议重点是探讨先进制造和封装。

其中,光刻机一哥ASML(阿斯麦)的研发副总裁Anthony Yen表示,EUV光刻工具是目前唯一能够处理7nm和更先进工艺的设备,EUV技术已经被广泛认为是突破摩尔定律瓶颈的关键因素之一。

Yen援引统计数据显示,截至2019年第四季度,ASML当年共售出53台EUV NXE:3400系列EUV光刻机,使用EUV机器制造的芯片产量已经达到1000万片。他说,EUV已经成为制造7nm、5nm和3nm逻辑集成电路的最关键武器。

Yen还指出,三星电子于2020年3月宣布正式采用EUV光刻设备制造10nm DRAM芯片,预计2021年将大量使用这些设备来支持先进的DRAM工艺。

台积电研发副总裁Doug Yu则在会上提及,Chiplet小芯片系统封装技术被认为是扩展摩尔定律有效性的另一种武器,它认为Chiplets可以促进芯片集成、降低研发成本、提高成品率和实现高性能计算以及设计和架构创新。Yu透露,台积电开发了LIPINCONTM(低压封装互连)技术,数据传输速度为8GB/s/pin,旨在优化芯片的性能。

除前端工艺技术外,台积电还热衷于开发先进的封装工艺,最新的3D SoIC封装技术将于2021年进入批量生产,这将促进高性能芯片的成本效益生产。

值得一提的是,Intel院士Ravi Mahajan援引Yole的统计数据称,2024年先进的封装市场规模将增长到440亿美元,这促使Intel加紧在2.5D和3D封装业务中的部署。

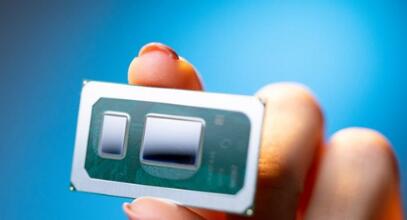

Intel所谓的2.5D封装即EMIB多芯片互联,封装尺度目前是55nm,3D封装则是Foveros,尺度50nm、Intel正致力于将EMIB推进到30-45 nm,3D Foveros推进到20~35nm。

- •台积电股价突然下跌4%:AI热潮背后,市场开始担心什么2026-03-11

- •台积电「双喜临门」:市值破兆、营收与股息齐飞,AI时代的战略落地2026-02-27

- •台积电Q4营收爆表!AI需求狂潮助力,营收大超预期!2026-01-14

- •突发!台积电数千晶圆瞬间报废,美国工厂单季利润暴跌99%2025-11-26

- •台积电被曝报复性开除员工?全球芯片巨头人事地震!2025-11-13

- •台积电获中日政府108.4亿元补贴,同比暴涨5.74倍!2024-03-07

- •ADI扩大与台积电的合作,提高供应链产能和韧性2024-02-23

- •ASML全年净销售额增30.2%,2030冲击0.7nm工艺2024-02-18

- •台积电或在日本建第二座工厂2024-01-29

- •从台积电2023财报看2024芯片行业发展趋势2024-01-25