富士通半导体推出顶尖定制化SoC创新设计方法

来源:华强电子网 作者:—— 时间:2014-01-15 10:48

富士通半导体(上海)有限公司今日宣布,成功开发了专为先进的28 nm SoC器件量身打造的全新设计方法,不仅能实现更高的电路密度,同时也可有效缩短开发时间。采用全新设计方法能够将电路的密度提高33%,并可将最终的线路布局时间缩短至一个月。这种设计方法将整合至富士通半导体的各种全新定制化SoC设计方案中,协助客户开发RTL-Handoff SoC器件。富士通半导体预计自2014年2月起将开始接受采用这种全新设计方法的SoC订单。

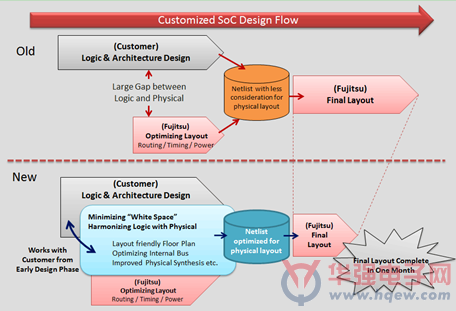

采用28nm等顶尖制程工艺的SoC器件需要有越来越多的功能与效能,进而要在芯片中布建越来越多的电路。未来SoC的设计将日趋复杂,开发时间也将会因此较以往增加,同时如何有效解决功耗问题也成为设计者的更大挑战。 为应对日趋复杂的SoC设计,富士通半导体所开发出的创新设计方法能实现更高的电路密度、更短的开发时程和降低功耗,并整合至富士通半导体的各种全新定制化SoC设计方案中,协助客户开发RTL-Handoff SoC组件。较传统的设计流程,设计者可采用富士通半导体的全新设计方法在相同大小的芯片中增加33%电路,而且可将最终的线路布局时间缩短至一个月。 全新设计方法将White Space有效最小化 全新的独家设计流程可估算出较容易布线的平面图,并根据布线路径与时序收敛为内部数据总线进行优化。这些设计步骤可将无法建置晶体管的White Space数量降到最少,因而可让芯片容纳更多电路。 透过专利技术协调逻辑与物理架构此专利技术无须更动任何逻辑设计,即可自动针对物理布线进行网表数据合成,并可提升整体设计的布线效率以及使时序收敛变得更容易,因而可有效减少最终布线流程所需的时间,更可达到更高的密度整合度。

图1:富士通半导体全新客制化SoC设计方法示意图

相关文章

- •如何搭建一个安全的网络监控中心2019-01-23

- •Marvell推全新ARMADA超大规模虚拟SoC2016-06-02

- •联发科三款处理器齐发:三卡三待来了!2016-01-26

- •2016年Marvell聚焦新业务,MoChi架构芯片终端即将落地2016-01-22

- •Silicon Labs Michele Grieshaber:物联网将成为下一波创新浪潮2016-01-19

- •物联网:多协议集成将推动物联网浪潮涌动2016-01-18

- •TI推出业内首款支持数字和模拟位置传感器的工业驱动控制片上系统 (SoC)2015-11-24

- •美高森美全新Libero SoC v11.6软件为其获奖FPGA器件 SmartFusion2 SoC 和 IGLOO2 增强易用性2015-10-28

- •基于多核异构的SoC 为工业4.0应用带来卓越的运算和实时控制能力2015-10-20

- •ARM为主流嵌入式SoC设计提供免费的Cortex-M0处理器IP2015-10-15