基于LVDS的高速图像数据存储器的设计与实现

来源:华强电子网 作者:------ 时间:2014-06-26 15:02

2 硬件电路设计

2.1 LVDS长线传输电路设计

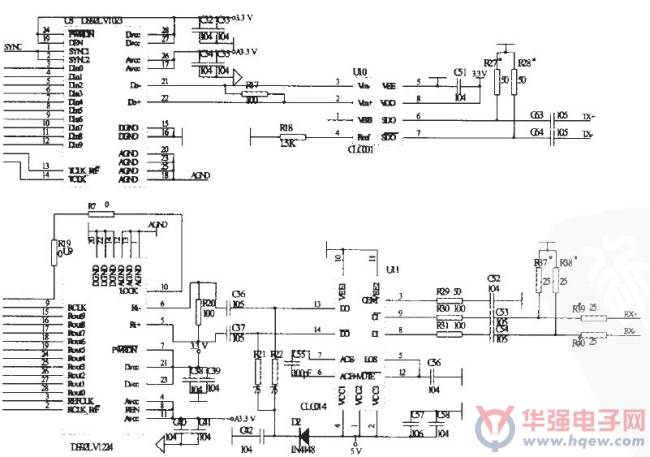

本设计系统中摄像头发出的视频图像信号属于高速变化的信号,容易受到噪声影响。低压差分(Low Volt-age Differential Signaling,LVDS)数据传输技术是一种新型的、具有很低的差分电压摆动幅度的信号传输方式。LVDS传输过程中以差分的方式传送数据,从而具有很低的串扰和噪声以及只消耗很少的功率。此外它通过一对并行PCB走线或平衡电缆传输数据,可以达到100 Mbit/s甚至高于1 Gbit/s的高速率数据传输。解决了高速数据的有效传输,同时也将有助于降低系统设计复杂度,提高系统可靠性。基于LVDS技术的传输特点及应用优势,本设计中图像输入接口采用LVDS进行图像数据接收。设计中为满足信号实时高准确性的传输,在LVDS发送端采用串化器和驱动器相结合的方式增强信号;在LVDS接收端采用均衡器和解串器相结合的方式,来补偿信号长线传输过程中的损耗。这样高速图像信号可以稳定地传输上百米。如图3为LVDS接口端硬件电路设计图。

图3 LVDS接口端硬件电路设计图

(点击查看大图)

2.2 FIFO的电路设计

本设计中进入FIFO前经解码得到的图像数据传输速率为30.72 Mbit/s,因此在FIFO的选型中,必须选择一款读写速度快而且容量大的外部FIFO来缓存图像数据。经过计算并对比分析后,本设计选用了CYPRESS公司生产的64 kbit x 18 bit的CY7CA285V:

1)CY7C4285V拥有66.7 MHz的最大工作频率,10 ns的最小读写周期,完全可以稳定、可靠地接收码率为30.72 Mbit/s的图像数据,也满足25 ns读写周期的要求。

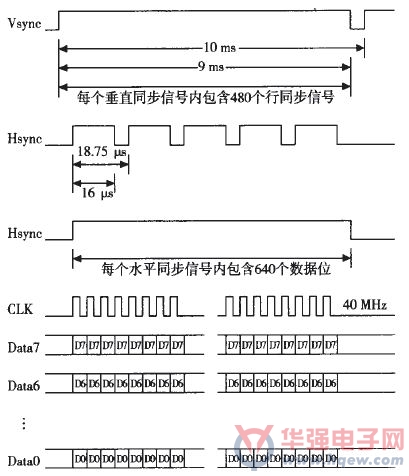

图4单路图像数据接收接口时序定义图

2)从FIFO接收图像数据的时序图中(如图4)可以看出,一个水平同步时间内,写入FIFO的图像数据有640 byte,而读出FIFO的数据量为33 Mbyte/s x 18.75 μs=618.75 byte。这样每一个水平同步时间内FIFO中就会剩余640 byte-618.75 byte=21.25 byte的图像数据。当垂直同步信号拉低时,FIFO中剩余的图像数据量达到最大,本设计FPGA控制FIFO半满即读,那么FIFO的容量至少应为:2 x 21.25 x480=20400 byte。显然容量为64 kbyte的CY7C4285V可以满足设计要求。

3)操作简单。首先,单片64 kbyte CY7CA285V就可以满足设计要求,而不需串联多个FIFO,这样操作起来方便了很多。其次,该FIFO有读使能、写使能作为状态保障,且均采用边沿触发方式,使得时序控制简捷高效,便于FPGA的逻辑实现。

- •受iPhone6拉货影响 NAND第三季可望摆脱供过于求2015-05-14

- •2014年第四季NAND Flash品牌供货商营收季增2%,2015年第一季将供过于求2015-02-05

- •原厂价格战暂歇,12月上旬NAND Flash合约价维持缓跌走势2014-12-16

- •2015年NAND Flash产业持续向上,产值成长超过10%2014-12-04

- •OEM需求拉货动能增温,第三季NAND Flash品牌营收季增12.2%2014-11-11

- •iPhone6/6Plus将带动智能型手机NAND Flash搭载量的规格竞赛2014-10-24

- •盛群推出适合AC电源应用的Flash MCU2014-09-28

- •2015年NAND Flash市场规模将达266亿美元 年成长9%2014-08-27

- •NAND Flash价格年跌28% 产能竞争加速2014-08-18

- •第二季NAND Flash品牌供货商营收达76.49亿美元 季增5.6%2014-08-14