如何采用门控时钟来设计低功耗时序电路

来源:华强电子网 作者:------ 时间:2014-07-03 14:13

典型时序电路的缺陷

如图1所示,这种电路最大的缺点是不可配置,因此,不能改变时钟分频因子。一个N触发器设计只能产生2N个周期的时钟。需要预先将固定数量的触发器加入到设计中,才能产生固定周期的时钟。这大大阻碍了特定时钟的设计,而且多个这样的设计,需要多种分频因子来进行分频。

另外,该设计非常耗能,并且也没有机制可通过高效门控时钟来节省动态功耗。如表1所示,Q3只能在时钟脉冲2和时钟脉冲6中改变其输出,对于所有其他时钟而言,触发器一次又一次地存储了相同的数据。这导致在时钟周期内产生了不必要的功耗,而采用适合的门控时钟可解决该问题。

通过调整结构和门控时钟来增强电路

任何时序电路都可通过调整结构和有效的门控时钟加以增强。图1中所示的约翰逊计数器在图2种得到了增强,可以灵活地支持多种分频因子,产生可变化的输出频率。

为了使其可编程,触发器的多个延迟阶段都加入了所需的组合逻辑,以根据所需分频因子进行选择。

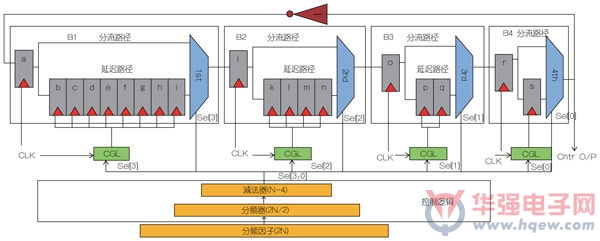

图2显示的就是一款低功耗可编程约翰逊计数器。该电路包括级联延迟阶段B1、B2、B3、B4、逆变器I、参考时钟输入CLK、门控时钟逻辑CGL,以及控制逻辑(分频器和减法器),可根据要求选择触发器组合。

图2:低功耗多级可编程约翰逊计数器

在图2所示的修改后的约翰逊计数器电路中,我们采用了19个D触发器,这些触发器提供8至38以内的偶数值的分频因子。可通过添加额外的触发器和多路复用器,使所需分频因子进一步增加至任何偶数值。多个路径可将触发器 “a、j、o和r” 的输出连接至相应的多路复用器输入,例如,分流路径将触发器 “a”的输出连接至第一个多路复用器的第一个输入,延迟路径则将触发器“a”的输出[经过一组触发器(b、c、d、e、f、g、h、i)]连接至第一个多路复用器的第二个输入。这种实施方案允许选择多路复用器输出,使电路具备所需的可配置性,可以支持多个分频因子。

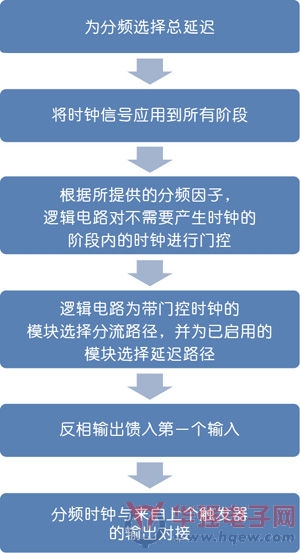

如图3所示,为了节省功耗,控制电路输出馈入CGL中,以根据所需分频因子启用或禁用“延迟路径触发器”的时钟。当分频因子为2N时,需要N个触发器提供所需的时钟频率。为了促进多路复用器输入的选择,并为时钟门控逻辑启用所选的输入,我们添加了一个主要由减法器构成的控制逻辑。该减法器可根据用户所提供的分频因子,将N-4作为输出提供,并且减法器(sel[3:0])的二进制输出位数每个都可作为4个多路复用器(1st、2nd、3rd、4th)的相应选择线路,并使CGL以高效的方式对触发器的时钟进行门控。

这有效地实现了设计的可编程化,并降低了计数器的动态功耗。

图3:电路运算说明图

- •【会议议程】12月19-21日2022(十四届)传感器与MEMS产业化技术国际研讨会(暨成果展)佛山南海瞻云酒店召开2022-12-16

- •FORESEE XP1000 PCIe SSD开启Gen3后时代发展之路2021-08-02

- •FORESEE工规级SSD应用宽温技术,加速智能工业场景落地2021-07-21

- •基于J750EX测试系统的SRAM VDSR32M32测试技术研究2017-09-05

- •Vishay检查表: 采用安规电容防止过载的12点注意事项2017-07-28

- •汽车系统的USB供电2017-06-08

- •适用于 FPGA、GPU 和 ASIC 系统的电源管理2017-05-11

- •一文读懂SPI串行外设接口2017-04-27

- •TLV3501滞回比较器电路设计2017-04-14

- •ZigBee无线呼叫系统硬件电路2017-04-05