Synopsys新标准单元库和存储器套件 为SoC所有处理器内核实现最优化平衡

来源: 作者:yuhongda 时间:2013-06-26 17:27

“DesignWare HPC(高性能内核)设计套件可使SoC设计师优化其片上CPU、GPU和DSP IP内核,根据我们与重要合作伙伴(如Imagination Technologies、CEVA和芯源科技)紧密合作开发的成果显示,可使主CPU内核的性能提高达10%,GPU内核功耗降低达 25%、面积缩小达10%。”在6月24日深圳媒体见面会上,Synopsys逻辑库产品市场经理Ken Brock将这款最新产品的卓越性能和技术特点为我们做了详细介绍。

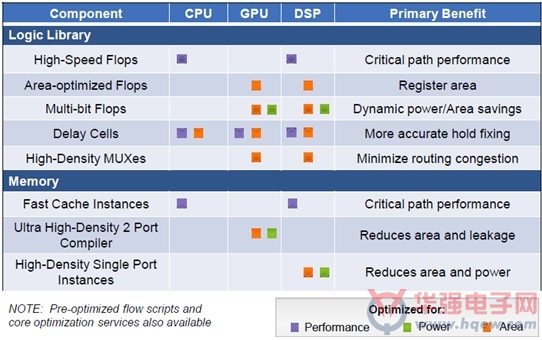

作为DesignWare? Duet嵌入式存储器以及逻辑库IP组合的扩展,此次发布的全新DesignWare HPC设计套件包括包括超高密度的存储器编译器和超过125种全新的标准单元和存储器实例,可优化一个系统级芯片(SoC)上的所有处理器内核,以实现最大的速度、最小的面积或最低的功耗,或针对其特殊的应用需求实现上述三者的最优化平衡。通过Synopsys的FastOpt服务,在短短的四到六周内即可实现优化的处理器内核。应用于28nm工艺的DesignWare HPC Design Kit设计套件将于7月开始供货。HPC设计套件所包括的各组件及其主要功效如下图所示。

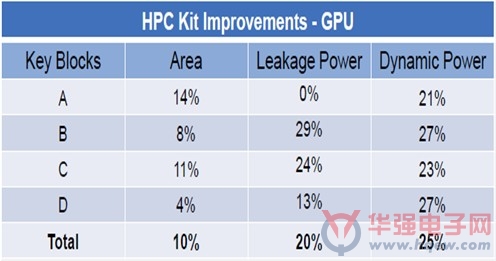

Ken Brock通过与Imagination合作的最新案例 PowerVR? Series6 GPU,向记者进一步分析了该设计套件的性能特点。PowerVR? Series6 GPU中包括了超高密度存储器、数据通道库 、全新标准单元、杠杆式的多比特触发器等物理IP单元,从而使面积和能效得到显著提升。据Synopsys业务拓展总监 江伟杰介绍,在智能手机、平板电脑等移动终端中,GPU所占比例一般在40%左右,因此能够使一颗芯片的成本节省约0.25美元。

Imagination Technologies 负责IMGworks SoC设计的执行副总裁Mark Dunn表示道,“使用Synopsys公司的HPC Design Kit高性能内核设计套件的标准单元和存储器来构建PowerVR? Series6 GPU,从整体上将动态功耗减少高达25%,同时面积缩小高达10%,其中的一些模块的面积改善达到了14%。我们还创建了一个经过调整的设计流程,该设计流程已经使得实现周期改善了高达30%。”

使用HPC Design Kit设计套件的PowerVR? Series6 GPU

Synopsys多样化的DesignWare IP包括经过硅验证的嵌入式存储器编译器和标准单元库,它们支持一系列从180纳米到28纳米的晶圆代工厂和工艺,并已经成功地应用在超过三十亿只已发货的芯片之中。DesignWare Duet嵌入式存储器和逻辑库套件包含了实现一个完整的SoC所需的所有物理IP单元,包括标准单元、SRAM编译器、寄存器文件、ROM、数据通道库和功率优化包(POK)等。并提供了过驱动/低电压工艺、电压温度(PVT)角、multi-channel单元、存储器内建自测和修复等选项。为满足先进CPU、GPU和DSP内核在速度和密度上的特殊要求,DesignWare HPC设计套件添加了为此而在性能、功耗和密度等方面进行了优化的标准单元以及存储器实例。

HPC设计套件包括快速缓存存储器实例和性能经调整的触发器,它们可实现比标准Duet套件高出达10%的速度提升。为了使动态和漏电功耗以及芯片面积减少到最小,新的套件提供了面积优化的触发器、多比特触发器和一种超高密度二端口SRAM,实现了高达25%的面积缩小和功耗降低,同时保持了处理器的性能。

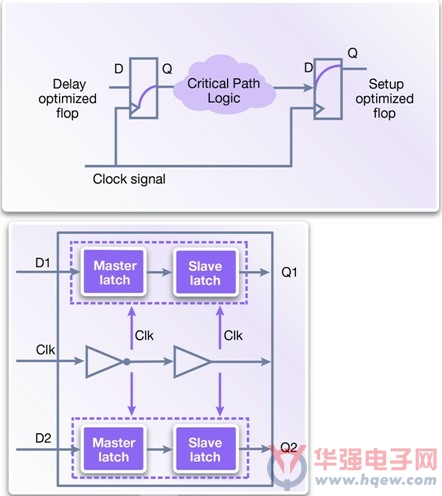

Ken Brock对该设计套件的一些主要技术细节也进行了介绍。性能经调整的多个触发器的组合能够根据应用需求进行针对性的优化。延迟优化和设置优化触发器管理关键的逻辑路径,对性能提升有显著作用,多比特触发器时钟载入,能使芯片面积和泄漏功耗降到最低。

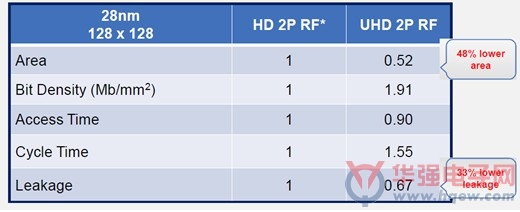

在智能手机,平板电脑,数字电视和数据通信应用中,使用超过密度存储器的GPU能有效减少芯片面积和漏电功耗,以下是我们将超高密度的2端口RF 与 高密度的2端口RF进行的对比,芯片面积减少了48%,漏电功耗有效降低了33%。

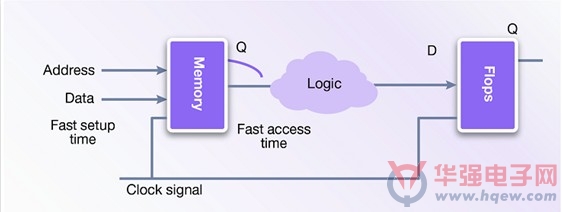

高速缓冲存储器实例的使用能让CPU的速度提高至10%,单端口存储器带来快速安装时间和访问时间,设置和访问时间的总和保持在较低水平,长通道器件的使用,以保持低泄漏功耗。

- •如何搭建一个安全的网络监控中心2019-01-23

- •三重富士通半导体股份有限公司推出55nm CMOS毫米波制程设计套件2018-01-29

- •先进的模拟CMOS设计套件支持一次设计成功2016-07-21

- •Marvell推全新ARMADA超大规模虚拟SoC2016-06-02

- •联发科三款处理器齐发:三卡三待来了!2016-01-26

- •2016年Marvell聚焦新业务,MoChi架构芯片终端即将落地2016-01-22

- •Silicon Labs Michele Grieshaber:物联网将成为下一波创新浪潮2016-01-19

- •物联网:多协议集成将推动物联网浪潮涌动2016-01-18

- •TI推出业内首款支持数字和模拟位置传感器的工业驱动控制片上系统 (SoC)2015-11-24

- •美高森美全新Libero SoC v11.6软件为其获奖FPGA器件 SmartFusion2 SoC 和 IGLOO2 增强易用性2015-10-28