如何采用门控时钟来设计低功耗时序电路

来源:华强电子网 作者:------ 时间:2014-07-03 14:13

在传统设计中,所有计算机运算(算法、逻辑和存储进程)都参考时钟同步执行,时钟增加了设计中的时序电路数量。在这个电池供电设备大行其道的移动时代,为了节省每一毫瓦(mW)的功耗,厂商间展开了残酷的竞争,因此将电路分成多个电源域并根据要求关闭它们,并且在设计每个时序电路的同时节省功耗,这两点至关重要。时序电路(如计数器和寄存器)在现代设计中无处不在。本文以约翰逊计数器为例介绍了如何采用有效门控时钟来设计高能效的时序电路。

约翰逊计数器系统,可同步提供多种特殊类型的数据序列,这对于大多数重要应用(如D/A转换器、FSM和时钟分频器)来说至关重要。为支持不同频率(从MHz 到 GHz)的模块,越来越多的IP集成到片上系统,因此,设计中在不同层级实施了许多可支持多个分频因子的时钟分频器。本文中,我们介绍了一款节能设计,即用带有门控时钟的多级可编程约翰逊计数器系统来取代多个时钟分频器,该计数器可提供8至任何偶数值(在本文中为38)的时钟分频因子。下面,我们将探讨实施细节和该技术的优劣。

典型时序电路

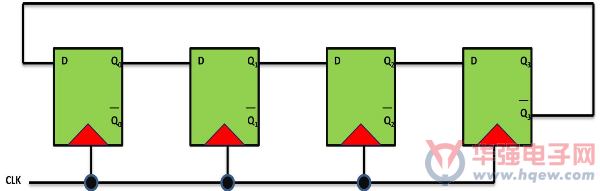

图1给出的是一款传统4位上升沿约翰逊计数器。约翰逊计数器只不过是修改过的移位寄存器,其最后一个D触发器的反相输出作为第一个D触发器的输入。所有其他触发器将接收上一个触发器所提供的输出。

图1:传统约翰逊计数器

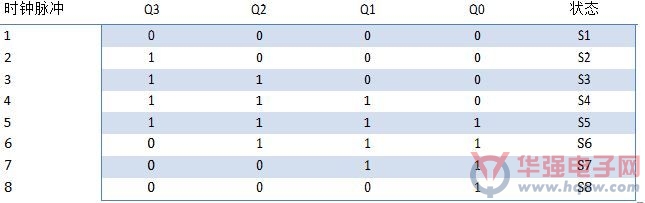

如表1所示,在所有的纵列中,4个连续的“0”后面都跟随着4个连续的“1”,但所有纵列都位于不同的阶段。约翰逊计数器可同步创建一个特定的数据模式。该数据模式在建模时非常有用,因为它可以使用任何抽头就可以产生一个有不同阶段的时钟样式的模式。此外,从表中可以推导出,约翰逊计数器只使用了N个触发器提供2N个状态,因此,与标准环形计数器相比,约翰逊计数器仅需要一半数量的触发器便可实现同样的MOD。

表1:约翰逊计数器的状态表

- •【会议议程】12月19-21日2022(十四届)传感器与MEMS产业化技术国际研讨会(暨成果展)佛山南海瞻云酒店召开2022-12-16

- •FORESEE XP1000 PCIe SSD开启Gen3后时代发展之路2021-08-02

- •FORESEE工规级SSD应用宽温技术,加速智能工业场景落地2021-07-21

- •基于J750EX测试系统的SRAM VDSR32M32测试技术研究2017-09-05

- •Vishay检查表: 采用安规电容防止过载的12点注意事项2017-07-28

- •汽车系统的USB供电2017-06-08

- •适用于 FPGA、GPU 和 ASIC 系统的电源管理2017-05-11

- •一文读懂SPI串行外设接口2017-04-27

- •TLV3501滞回比较器电路设计2017-04-14

- •ZigBee无线呼叫系统硬件电路2017-04-05