16nm/14nm FinFET技术将开启电子行业的下一个飞跃

来源:华强电子网 作者:—— 时间:2013-04-11 10:42

如前所述,上述问题将影响影响定制/模拟设计。如果数字设计工程师能够利用自动化的,支持FinFET器件的工具和支持FinFET的单元库,他或她将发现,其工作上最大的变化将是单元库:更好的功耗和性能特性!但是,数字设计工程师也会发现新的和更复杂的设计规则,双图形着色的要求,和更加严格的单元和pin位置的限制。最后,有些SoC设计人员还会被要求来设计和验证上百万门级别的芯片。设计师将需要在更高的抽象层次上工作和大量重复使用一些硅IP。

EDA产业在研发上花费了大量的钱,以解决高级节点上设计的挑战,事实上,我们期望,EDA行业为了20纳米,16纳米和14纳米的总研发费用可能会达到十二亿美金到十六亿美金。从FinFET器件的角度来看,例如,提取工具必须得到提高,以便能处理Rs和Cs从而更好预测晶体管的性能。这些Rs和Cs不能等待芯片成型后分析 - 他们需要在设计周期的早期进行,所以电路工程师和版图工程师不得不工作得更加紧密,这也是方法学上很大的一个变化。

每个物理设计工具都必须能够处理几百条为了16nm/14nm FinFET技术而带来的新的设计规则。这包括布局,布线,优化,提取和物理验证。单元库也需要利用这些工具进行优化。所以一个整合了的先进节点的解决方案,将会使包括定制/模拟和数字设计的任务变得更加容易。

EDA供应商也是包括晶圆代工厂和IP供应商在内的垂直合作其中的一部分。从EDA和IP开发人员的反馈会影响进程的发展,这反过来又提出了新的要求的工具和IP。例如,在2012年,Cadence公司,ARM和IBM之间三方合作就产生了第一个14NM的FinFET器件的测试芯片。

16nm/14nm的FinFET技术将是一个小众技术,或进入IC设计的主流?历史证明,当新的创新出现,人们弄清楚如何使用它们来创新,往往会带来意想不到的价值。FinFET技术将启用下一个大的飞跃,为计算机,通信和所有类型的消费电子设备带来裨益。这就是为什么Cadence公司坚信FinFET技术将为电子行业开创一个新纪元,这也是为什么我们致力于为整个行业推进这项技术。

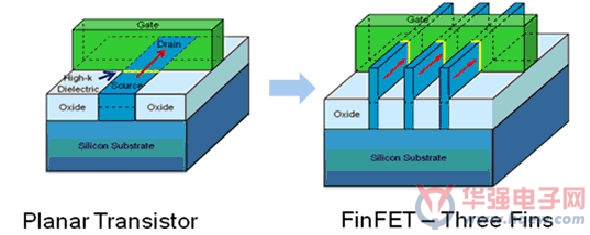

图表上相关英文词汇翻译:

Gate: 栅极

Drain:漏极

Oxide:氧化层

Source:源极

High Dielectric:高介质层

Silicon Substrate:硅衬底

Planar Transistor: 平面晶体管

FinFet- Three Fins:鳍型场效应晶体管——三鳍

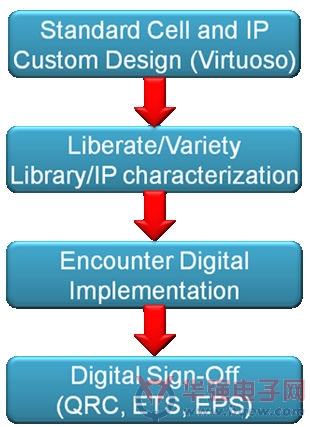

Cadence FinFet设计流程:

1.标准单元及IP设计

定制设计(Virtuoso)

2.标准单元及IP特征化

3. Encounter 数字实现

4. 数字设计签收(QRC, ETS,EPS)

- •Cadence 扩充系统 IP 产品组合,推出 NoC 以优化电子系统连接性2024-07-01

- •逆势高速增长!一家国内少有的IP+EDA新锐企业2023-09-11

- •EDA厂商华大九天成功登陆创业板2022-07-29

- •你不会以为EDA软件开发就只需要软件工程师吧?2022-07-11

- •突破EDA核心关键技术 概伦电子成功登陆科创板2021-12-28

- •EDA第一股来了!并购潮正式启动?2021-12-16

- •中国团队拿下EDA全球冠军!全网沸腾,国产EDA迎黄金时代2021-11-10

- •芯行纪宣布完成数亿元A轮融资,专注于数字实现EDA研发创新2021-10-29

- •比昂芯科技完成千万级天使轮融资,进一步优化EDA工具性能2021-10-11

- •华大九天首发上会 资本竞逐EDA 但这3家公司上市或存瑕疵2021-09-02